Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 177

UG366 (v2.5) January 17, 2011

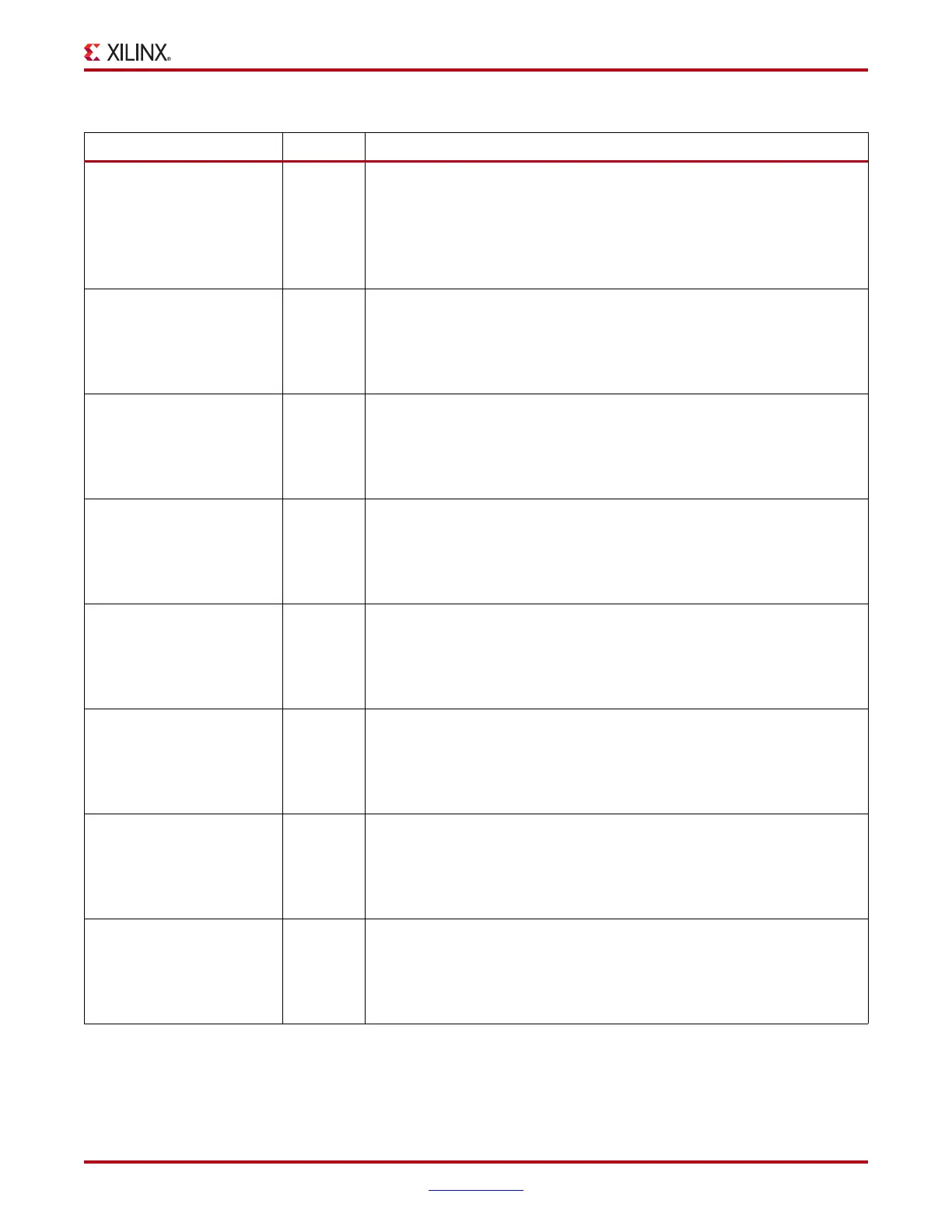

TX Configurable Driver

TX_DRIVE_MODE String This attribute selects whether PCI Express PIPE Spec pins or TX Drive

Control pins control the TX driver. The default is “DIRECT”.

DIRECT: TXBUFFDIFFCTRL, TXDIFFCTRL, and TXPOSTEMPHASIS

control the TX driver settings.

PIPE: TXDEEMPH, TXMARGIN, and TXSWING control the TX driver

settings.

TX_MARGIN_FULL_0[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 000 and

TXSWING = 0. TX_MARGIN_FULL_0 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1001110 (1040 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_FULL_1[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 001 and

TXSWING = 0. TX_MARGIN_FULL_1 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1001001 (850 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_FULL_2[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 010 and

TXSWING = 0. TX_MARGIN_FULL_2 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1000101 (515 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_FULL_3[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 011 and

TXSWING = 0. TX_MARGIN_FULL_3 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1000010 (290 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_FULL_4[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 100 and

TXSWING = 0. TX_MARGIN_FULL_4 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1000000 (130 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_LOW_0[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 000 and

TXSWING = 1. TX_MARGIN_LOW_0 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1000110 (590 mV

PPD

typical).

Do not modify this value.

TX_MARGIN_LOW_1[6:0] 7-bit

Binary

This attribute has the value of TXBUFFDIFFCTRL[2:0] and

TXDIFFCTRL[3:0] that has to be mapped when TXMARGIN = 001 and

TXSWING = 1. TX_MARGIN_LOW_1 = TXBUFDIFFCTRL[2:0],

TXDIFFCTRL[3:0]. The default is 7’b1000100 (445 mV

PPD

typical).

Do not modify this value.

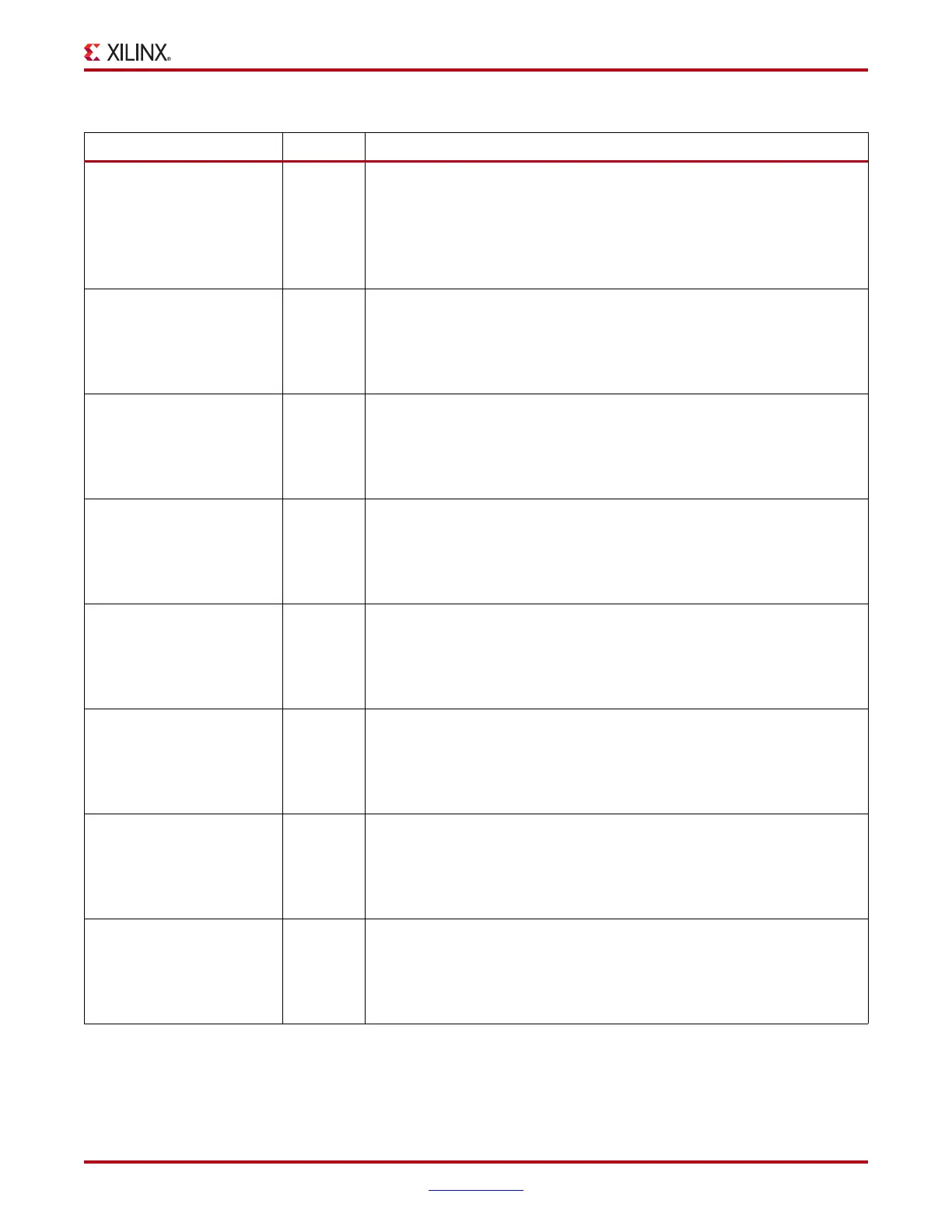

Table 3-32: TX Configurable Driver Attributes (Cont’d)

Attribute Type Description

Loading...

Loading...