176 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

Table 3-32 defines the TX configurable driver attributes.

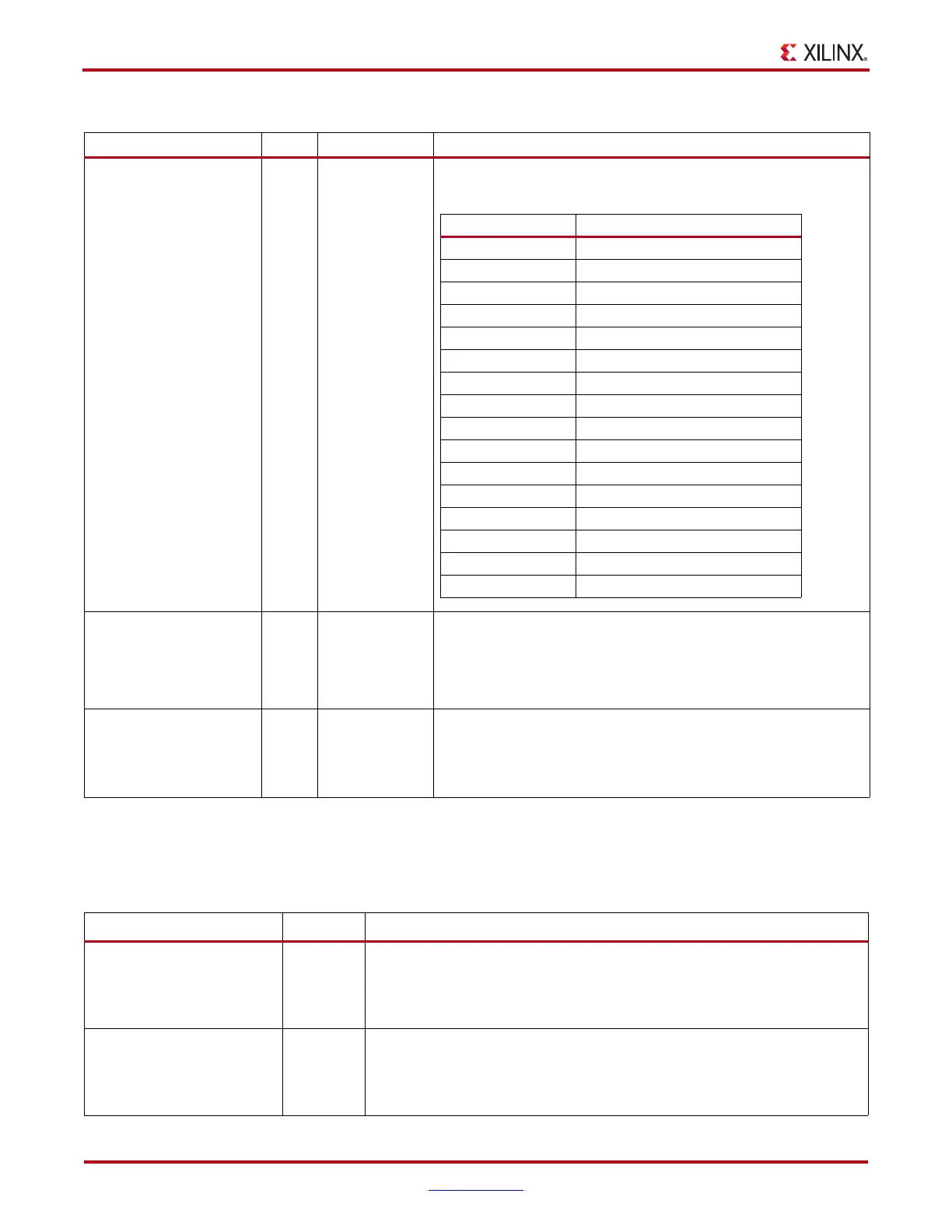

TXPREEMPHASIS[3:0] In Async Transmitter Pre-Cursor TX Pre-Emphasis Control

.

The default is

user specified. All listed values (dB) are typical.

TXP

TXN

Out

(Pad)

TX Serial Clock TXP and TXN are differential complements of one another

forming a differential transmit output pair. These ports represent

the pads. The locations of these ports must be constrained (see

Implementation, page 41) and brought to the top level of the

design.

TXSWING In Async TX swing control for PCI Express PIPE Interface

(1)

. This signal is

mapped internally to TXDIFFCTRL/TXBUFDIFFCTRL.

0: Full Swing

1: Low Swing

Notes:

1. As per PHY Interface for the PCI Express Architecture, PCI Express 2.0, Revision 0.5, August 2008.

Table 3-31: TX Configurable Driver Ports (Cont’d)

Port Dir Clock Domain Description

[3:0] dB (Pre-Emphasis Magnitude)

0000 0.15

0001 0.3

0010 0.45

0011 0.61

0100 0.74

0101 0.91

0110 1.07

0111 1.25

1000 1.36

1001 1.55

1010 1.74

1011 1.94

1100 2.11

1101 2.32

1110 2.54

1111 2.77

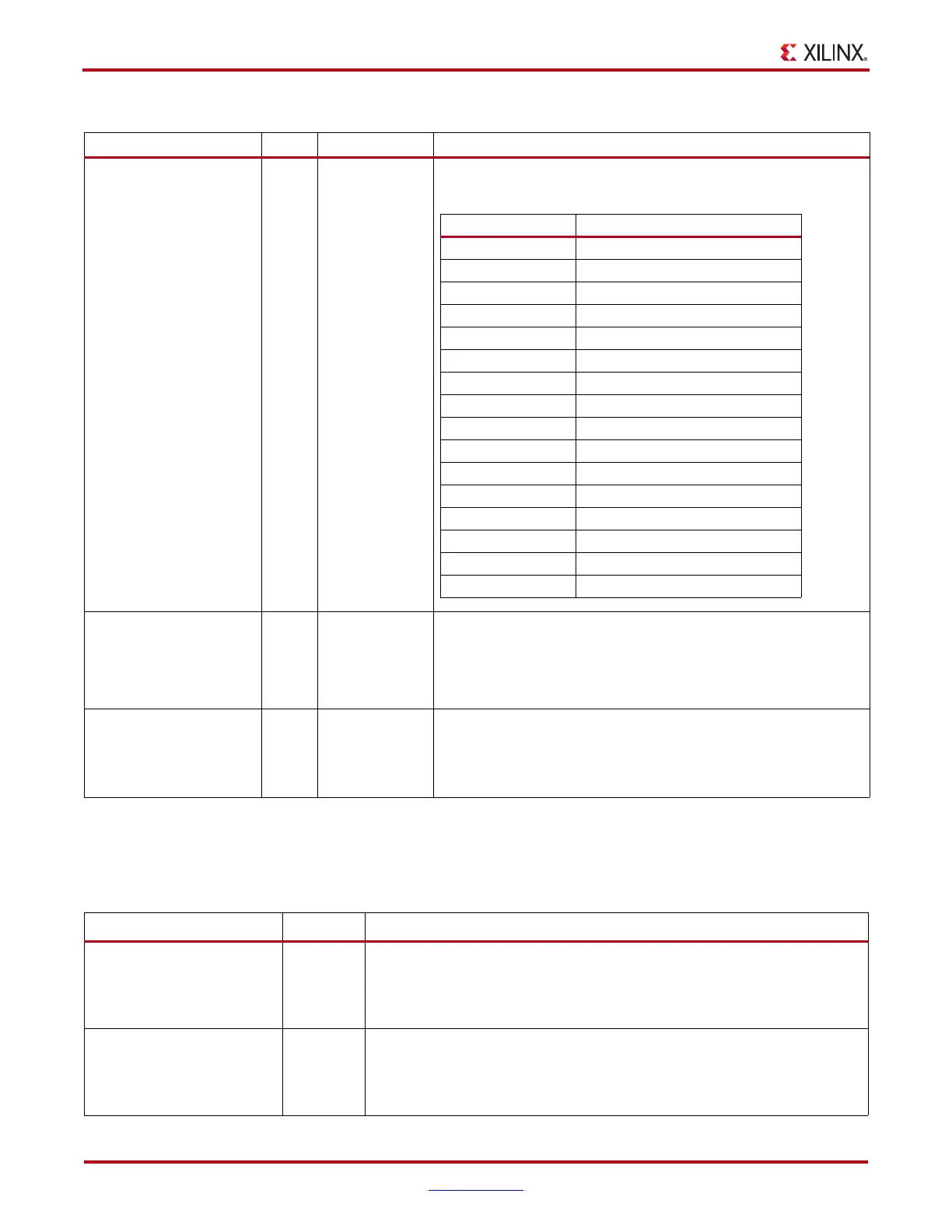

Table 3-32: TX Configurable Driver Attributes

Attribute Type Description

TX_DEEMPH_0[4:0] 5-bit

Binary

This attribute has the value of TXPOSTEMPHASIS[4:0] that has to be

mapped when TXDEEMPH = 0. TX_DEEMPH_0[4:0] =

TXPOSTEMPHASIS[4:0]. The default is 11010 (nominal value).

Do not modify this value.

TX_DEEMPH_1[4:0] 5-bit

Binary

This attribute has the value of TXPOSTEMPHASIS[4:0] that has to be

mapped when TXDEEMPH = 1. TX_DEEMPH_1[4:0] =

TXPOSTEMPHASIS[4:0]. The default is 10000 (nominal value).

Do not modify this value.

Loading...

Loading...