198 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

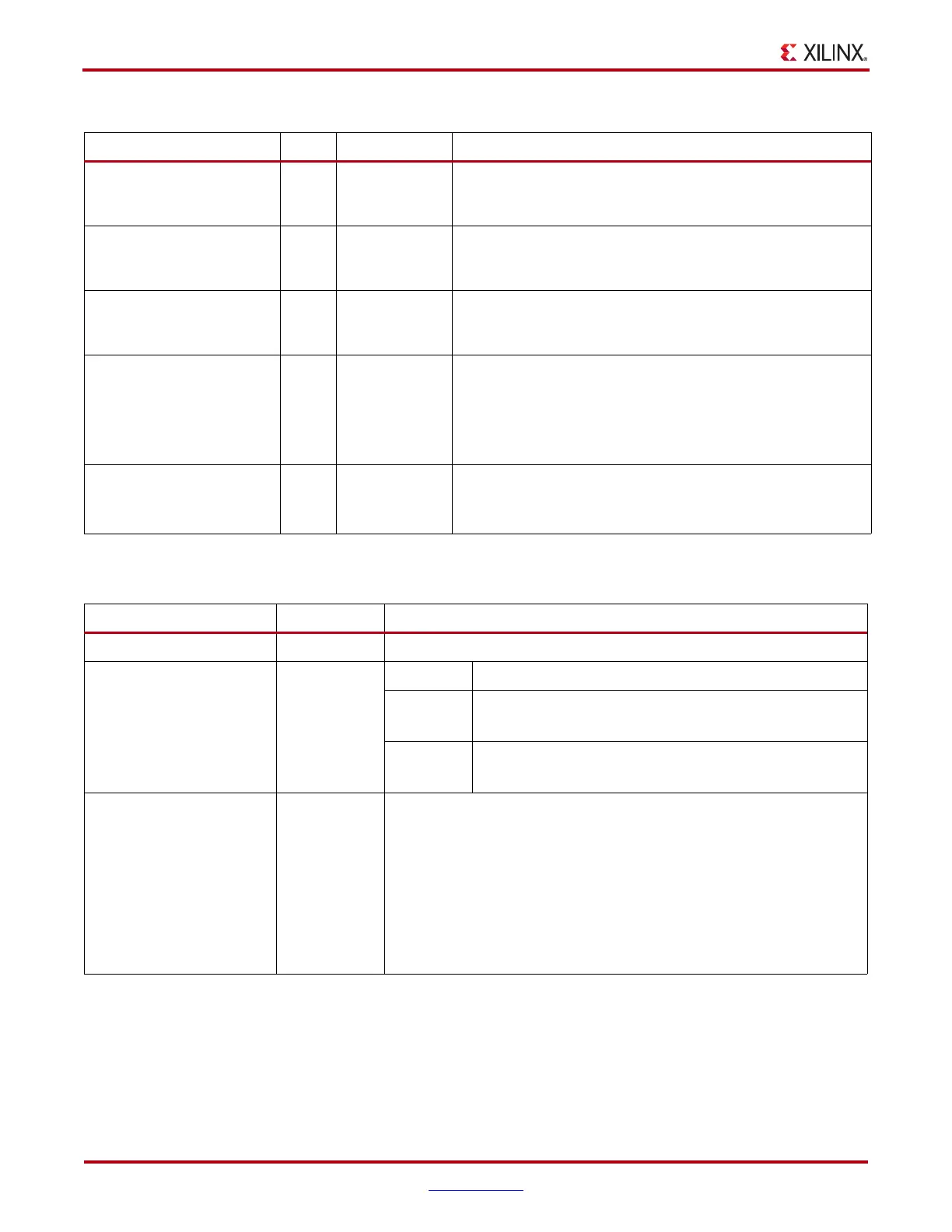

Table 4-12 defines the RX equalization attributes.

DFETAP3MONITOR[3:0] Out RXUSRCLK2 DFE tap 3 weight value monitor for each transceiver (3-bit

resolution plus 1-bit sign). For example, –2 is represented as

1 010.

DFETAP4[3:0] In RXUSRCLK2 DFE tap 4 weight value control for each transceiver (3-bit

resolution plus 1-bit sign). For example, –2 is represented as

1 010.

DFETAP4MONITOR[3:0] Out RXUSRCLK2 DFE tap 4 weight value monitor for each transceiver (3-bit

resolution plus 1-bit sign). For example, –2 is represented as

1 010.

DFETAPOVRD In RXUSRCLK2 Override enable for the DFE tap values.

0: Use the optimized DFE tap self-adapting values.

1: Override the DFE self-adapting values (recommended)

with the values provided by DFETAP1, DFETAP2,

DFETAP3, and DFETAP4.

RXEQMIX[9:0] In Async Receiver Equalization Control. Bits [9:3] are reserved. Only bits

[2:0] should be used.

The default is 3’b000, user specific.

Table 4-11: RX Equalizer Ports (Cont’d)

Port Dir Clock Domain Description

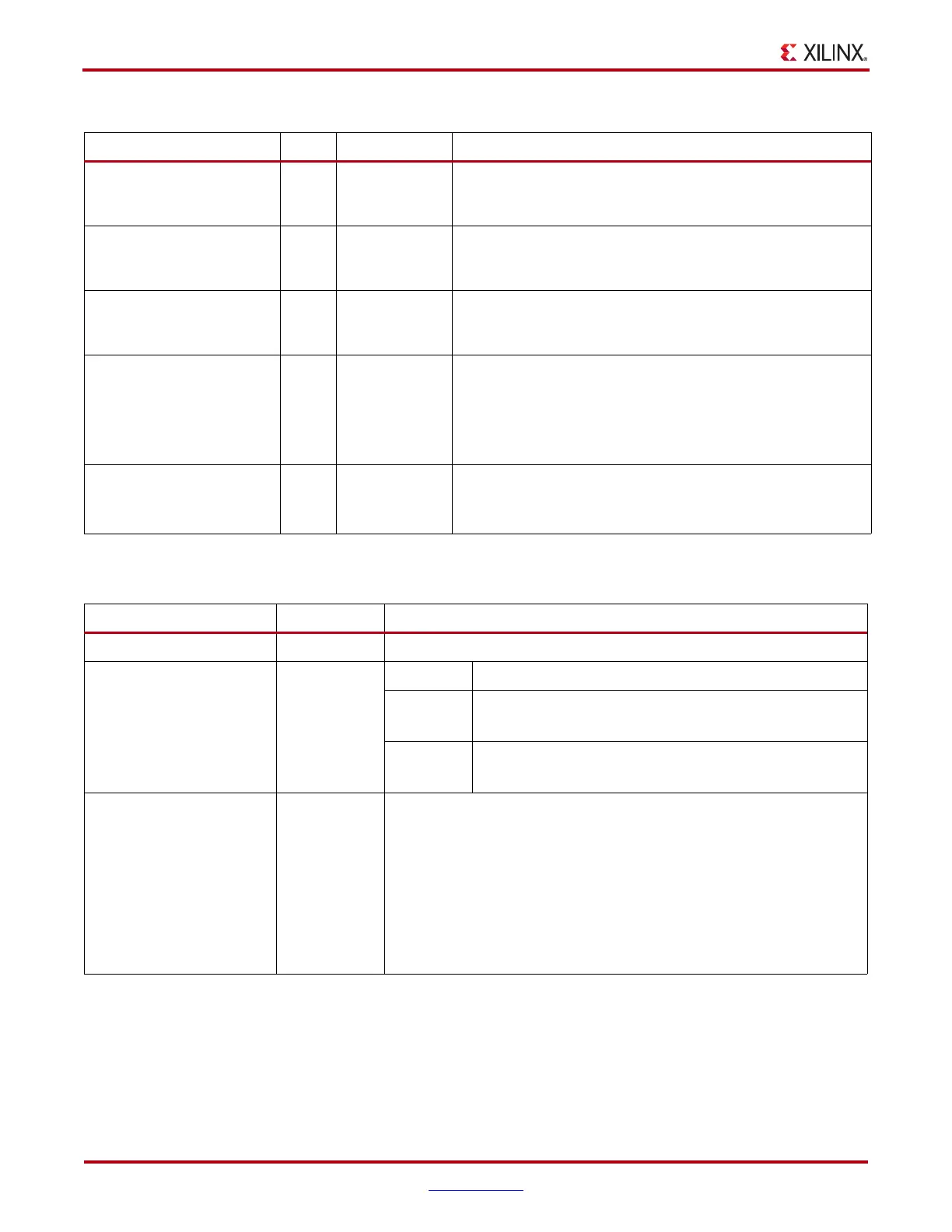

Table 4-12: RX Equalization Attributes

Attribute Type Description

DFE_CAL_TIME[4:0] 5-bit Binary DFE calibration time. Set to 01100 for normal operation (default).

DFE_CFG[7:0] 8-bit Binary DFE_CFG Description

[7:3] Limiter/EQAMP gain and power control

Set to 00011 (default)

[2:0] Vertical Eye measure AMP gain and power control.

Set to 011 (default)

RX_EN_IDLE_HOLD_DFE Boolean TRUE: Restores the DFE contents from internal registers after

termination of an electrical idle state for PCI Express operation. Holds

the DFE circuit in reset when an electrical idle condition is detected.

FALSE: (default)

Note: For channels with large attenuation (lossy channels typically

exceeding 15 dB at Nyquist), it is recommended that

RX_EN_IDLE_HOLD_DFE should be set to FALSE because fast

transitioning data patterns like the 101010 sequence in CJPAT/CJTPAT

can accidentally trigger an electrical idle

Loading...

Loading...