Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 233

UG366 (v2.5) January 17, 2011

RX Buffer Bypass

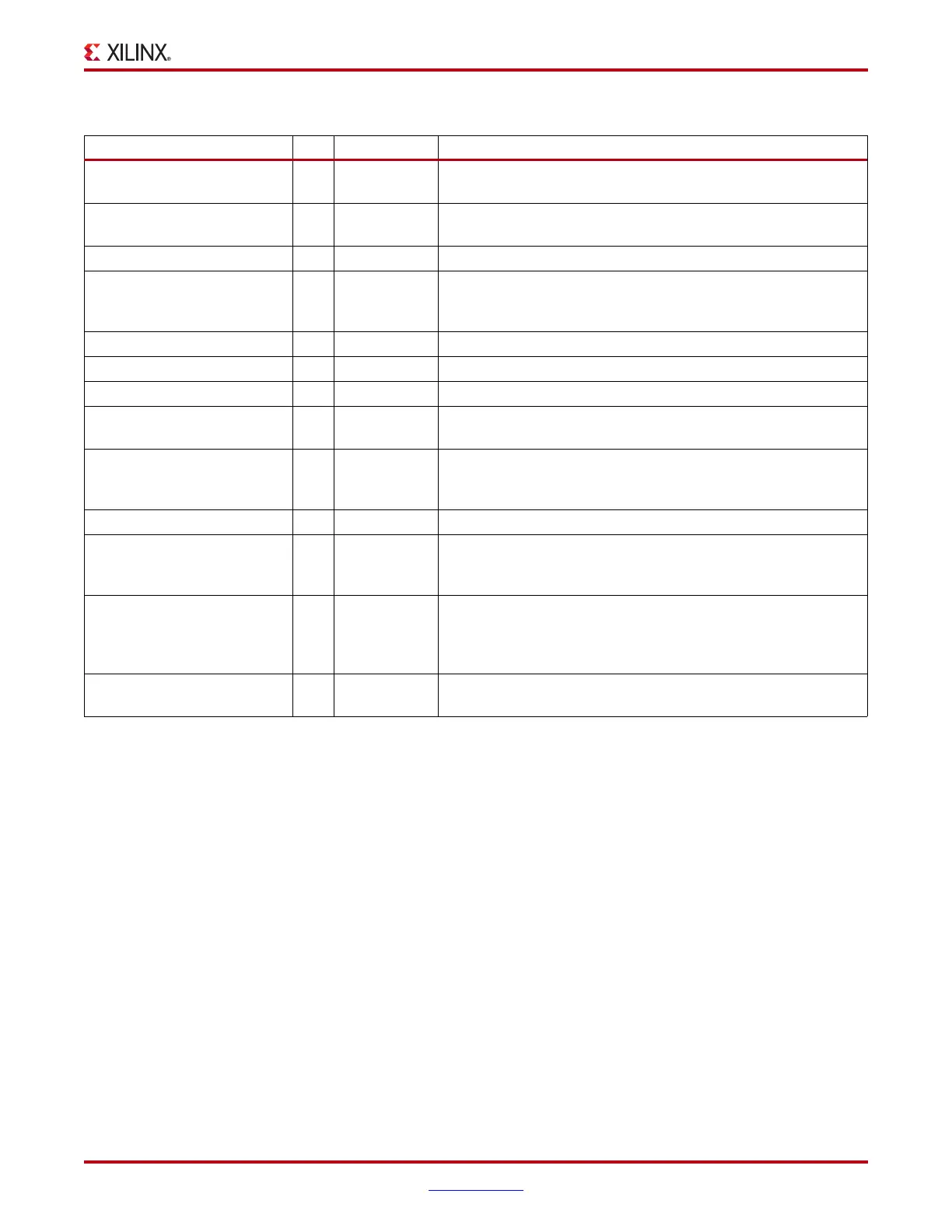

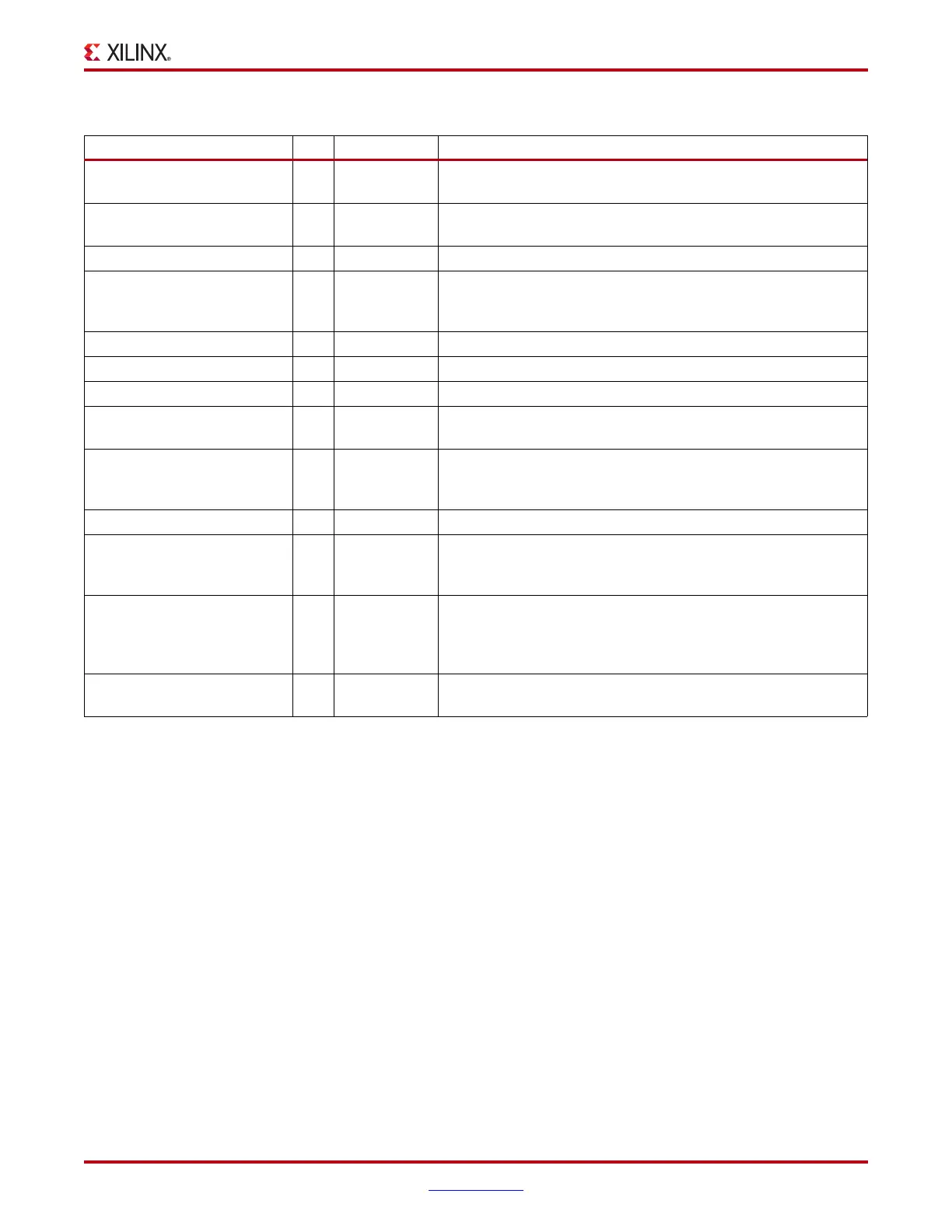

Table 4-40: RX Buffer Bypass Ports

Port Dir Clock Domain Description

RXDLYALIGNDISABLE In Async RX delay aligner enable/disable signal. When driven Low, it

enables the delay phase aligner.

RXDLYALIGNMONENB In Async RX delay aligner monitor enable/disable. When driven Low, this

port enables the RX delay aligner monitor.

RXDLYALIGNMONITOR[7:0] Out Async Reserved.

RXDLYALIGNOVERRIDE In Async RX delay aligner override. This port must always be tied High.

The delay value is set manually from the

RX_DLYALIGN_OVRDSETTING[7:0] attribute.

RXDLYALIGNRESET In Async Resets the RX delay aligner.

RXDLYALIGNSWPPRECURB In Async Reserved. It must be tied High.

RXDLYALIGNUPDSW In Async Reserved. It must be tied Low.

RXENPMAPHASEALIGN In Async When activated, the GTX receiver can align its XCLK with its

RXUSRCLK.

RXPLLLKDET Out Async Indicates that the VCO rate is within acceptable tolerances of the

desired rate when High. The GTX transceiver does not operate

reliably until this condition is met.

RXPLLLKDETEN In Async Enables the RX PLL lock detector. It must be tied High.

RXPMASETPHASE In Async When activated this pin aligns the PMA receiver recovered clock

with the PCS RXUSRCLK, allowing the RX elastic buffer to be

bypassed.

RXRECCLK Out N/A This is the recommended clock output to the fabric. The attribute

RXRECCLK_CTRL is the input selector for RXRECCLK and

allows the RX PLL input reference clock or the recovered clocks

to be output to fabric.

RXUSRCLK In N/A Use this port to provide a clock for the internal RX PCS datapath.

The rate for RXUSRCLK depends on RX_DATA_WIDTH.

Loading...

Loading...