UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 458 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

• If n is 32 or more, then all the bits in the result are cleared to 0.

• If n is 33 or more and the carry flag is updated, it is updated to 0.

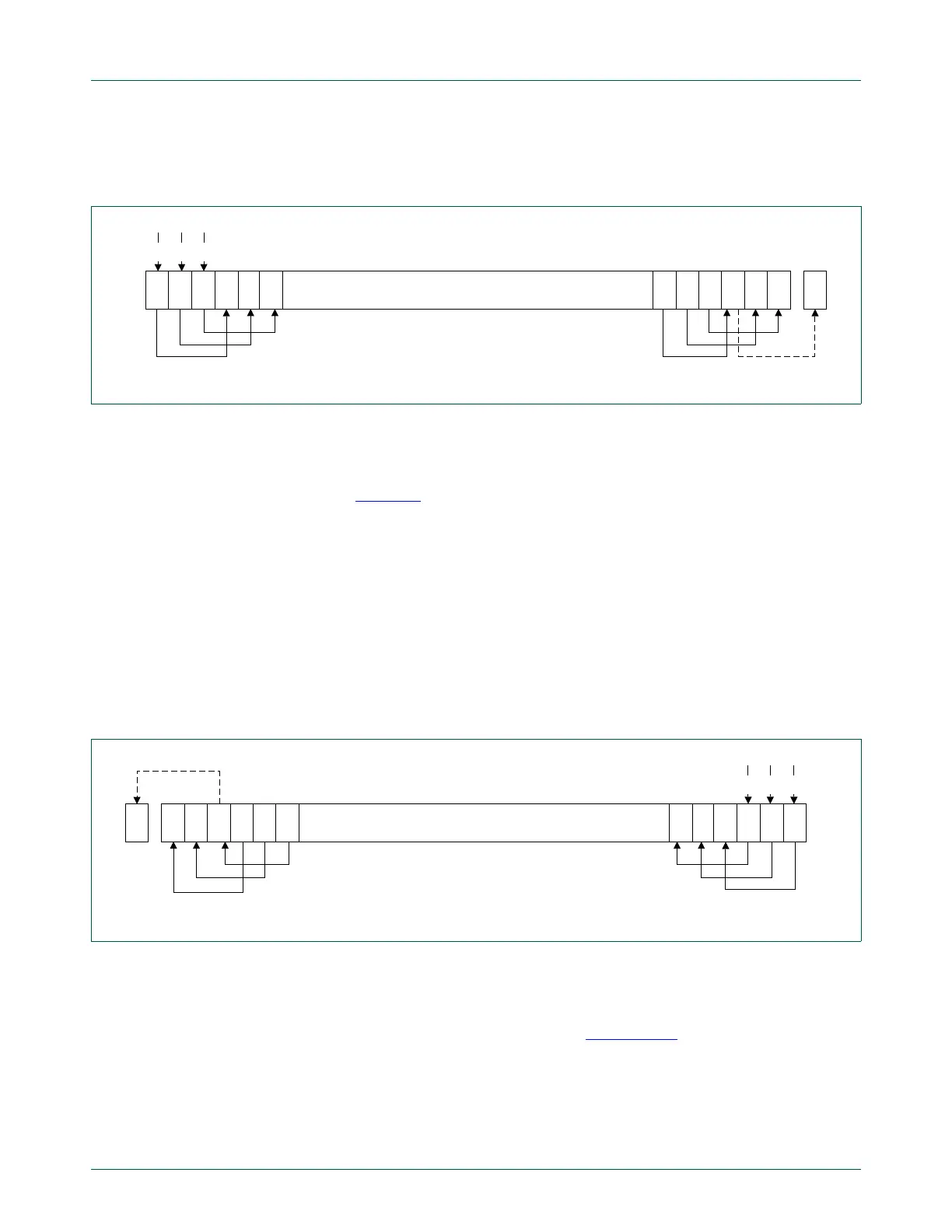

24.4.3.3.3 LSL

Logical shift left by n bits moves the right-hand 32-n bits of the register Rm, to the left by n

places, into the left-hand 32-n bits of the result, and it sets the right-hand n bits of the

result to 0. See Figure 84

.

You can use the LSL operation to multiply the value in the register Rm by 2

n

, if the value is

regarded as an unsigned integer or a two’s complement signed integer. Overflow can

occur without warning.

When the instruction is LSLS the carry flag is updated to the last bit shifted out, bit[32-n],

of the register Rm. These instructions do not affect the carry flag when used with LSL #0.

Remark:

• If n is 32 or more, then all the bits in the result are cleared to 0.

• If n is 33 or more and the carry flag is updated, it is updated to 0.

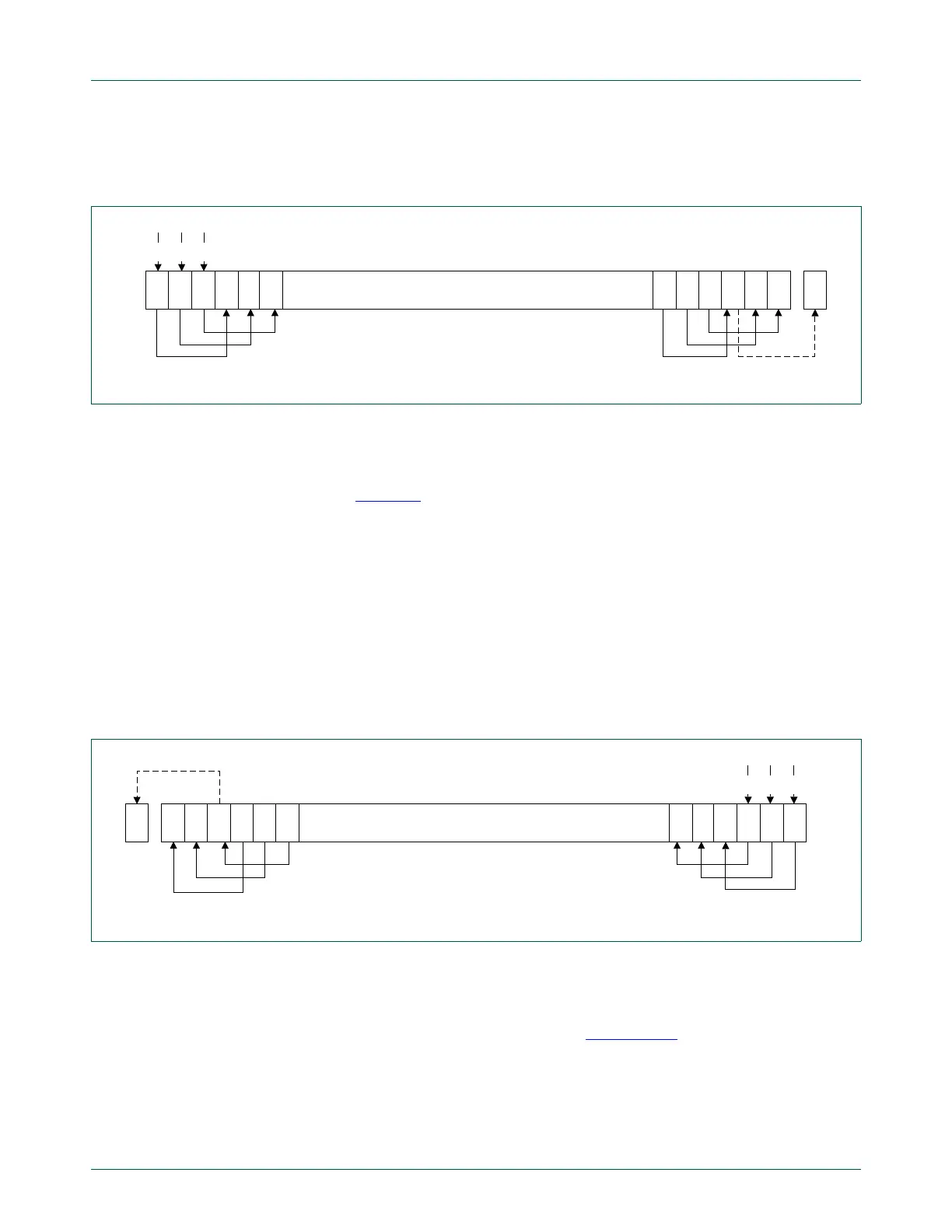

24.4.3.3.4 ROR

Rotate right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n

places, into the right-hand 32-n bits of the result, and it moves the right-hand n bits of the

register into the left-hand n bits of the result. See Figure 24–85

.

When the instruction is RORS the carry flag is updated to the last bit rotation, bit[n-1], of

the register Rm.

Remark:

Fig 83. LSR #3

&DUU\

)ODJ

Fig 84. LSL #3

&DUU\

)ODJ

Loading...

Loading...