190 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

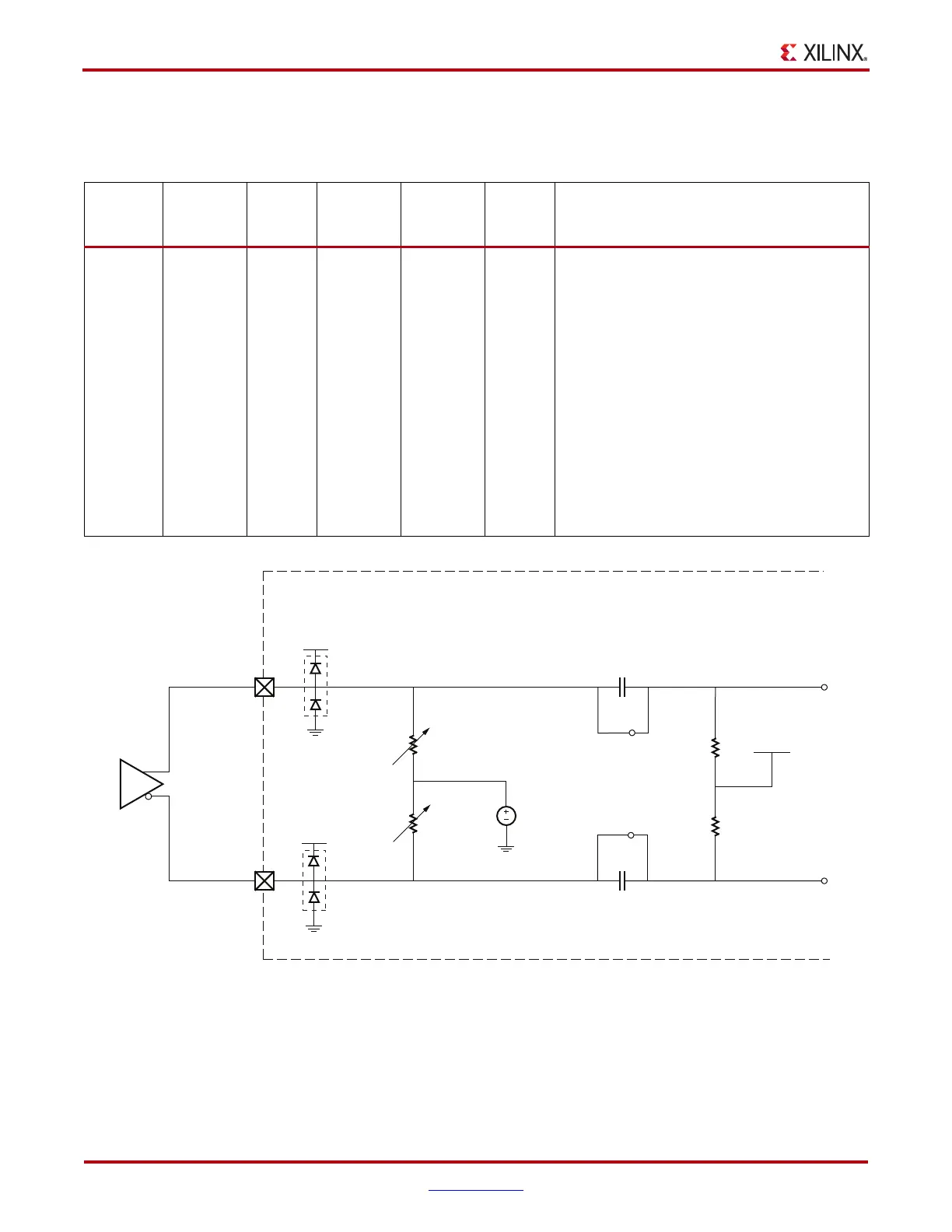

Table 4-7 outlines the recommended settings for RX termination in Use Mode 4. Figure 4-6

shows the Use Mode 4 configuration.

Table 4-7: RX Termination Use Mode 4 Configuration and Notes

Use Mode

External

AC

Coupling

Term

Voltage

Internal AC

Coupling

Internal

Bias

Max

Swing

mV

DPP

Suggested Protocols and Usage Notes

4OFFV

TT

OFF 800 mV 1200 Protocol: Custom GTX-GTX chip-to-chip

interface

Attribute Settings:

AC_CAP_DIS = TRUE

RCV_TERM_GND = FALSE

RCV_TERM_VTTRX = TRUE

Notes:

Recommended for use if the TX termination

voltage is 1.2V. If the TX termination voltage is

not 1.2V, DC current will result with possible

signal distortion. This allows for DC coupling

on the board. Not recommended for the

backplane due to interoperability with SerDes

where the TX termination voltage is not 1.2V.

X-Ref Target - Figure 4-6

Figure 4-6: RX Termination Use Mode 4 Configuration

UG366_c4_06_120909

nominal

50Ω

nominal

50Ω

FPGABoard

MGTAVTT_*

MGTAVTT_*

nominal 7 pFESD Diodes

ESD Diodes

nominal 7 pF

nominal

50 KΩ

nominal

50 KΩ

V

CM

2/3 MGTAVTT_*

MGTAVTT_*

Loading...

Loading...