310 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

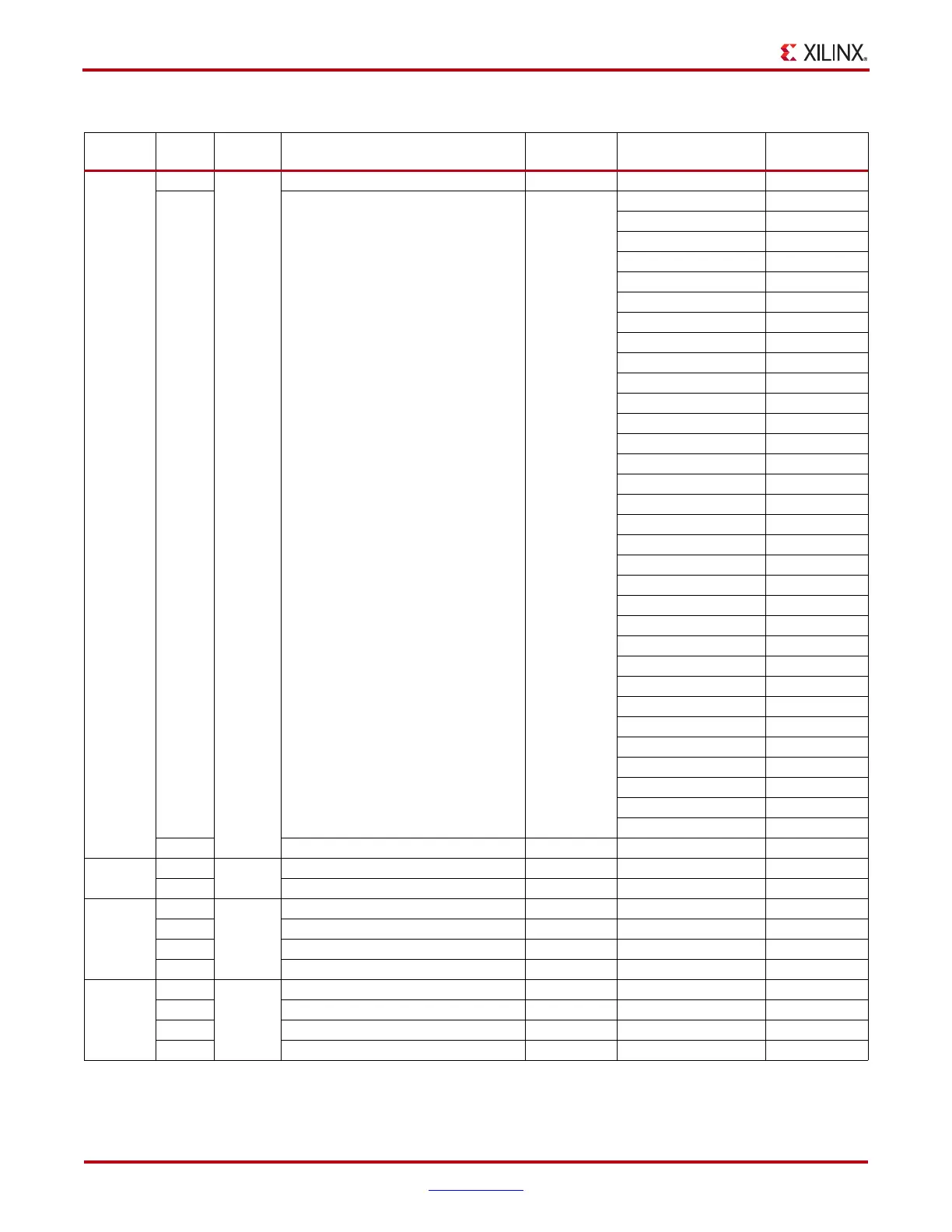

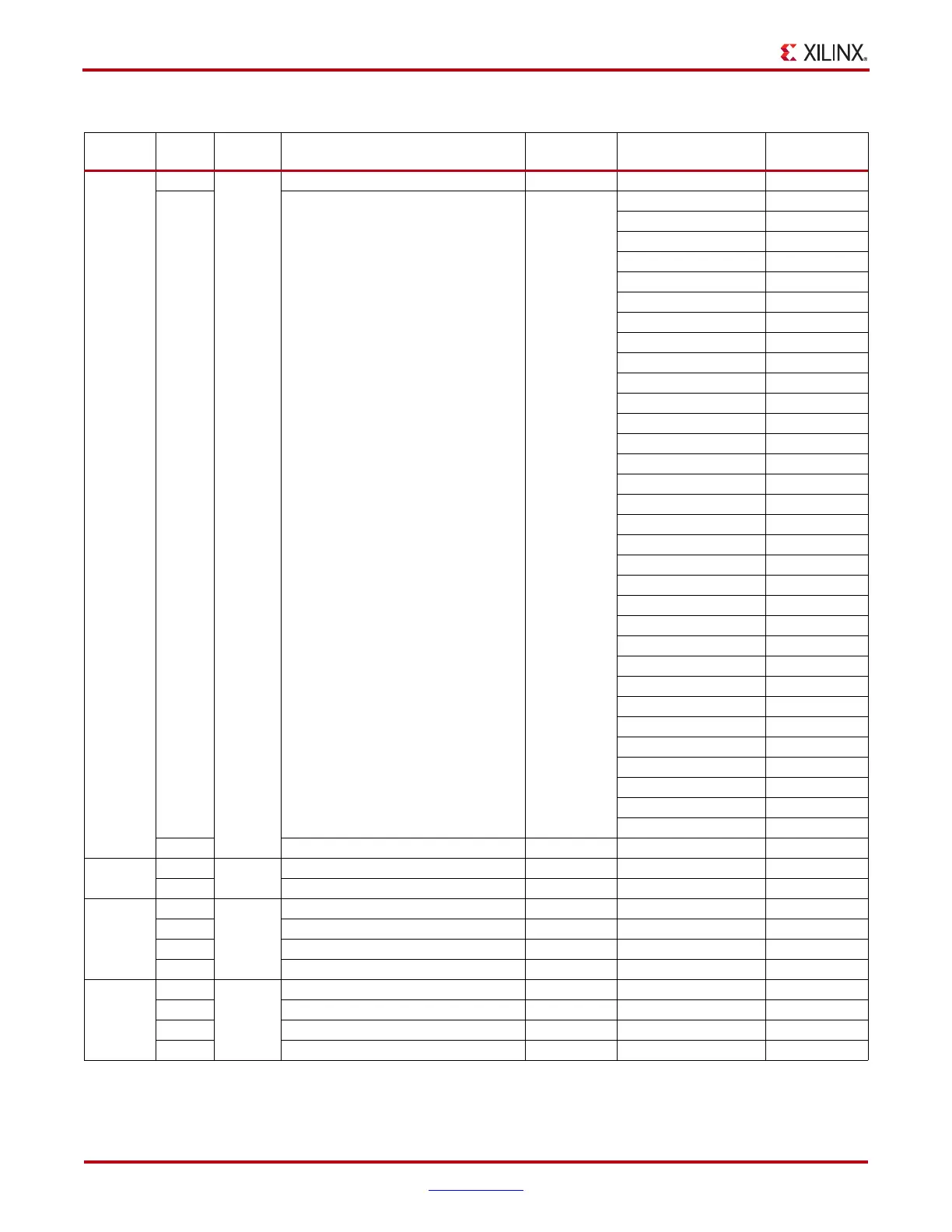

Appendix B: DRP Address Map of the GTX Transceiver

23h

15

R/W

Reserved

14:10 TX_CLK25_DIVIDER 4:0

6

00101

1 00000

2 00001

3 00010

4 00011

5 00100

7 00110

8 00111

9 01000

10 01001

11 01010

12 01011

13 01100

14 01101

15 01110

16 01111

17 10000

18 10001

19 10010

20 10011

21 10100

22 10101

23 10110

24 10111

25 11000

26 11001

27 11010

28 11011

29 11100

30 11101

31 11110

32 11111

9:0 TRANS_TIME_TO_P2 9:0

24h

15:12

R/W

COM_BURST_VAL 3:0 0-15

1

(1)

11:0 TRANS_TIME_FROM_P2 11:0

25h

15

R/W

TX_PMADATA_OPT 0-1

1

(1)

14:10 Reserved 4:0

9:8 CM_TRIM 1:0 0-3

1

(1)

7:0 TRANS_TIME_NON_P2 7:0

26h

15:14

R/W

BGTEST_CFG 1:0 0-3

1

(1)

13:12 TXPLL_SATA 1:0 0-3 1

(1)

11:6 SATA_MIN_WAKE 5:0 1-61 1

(1)

5:0 SATA_MAX_WAKE 5:0 1-61 1

(1)

Table B-1: Attributes DRP Address Map (Cont’d)

DADDR

DRP Bits R/W Attribute Name Attribute Bits Attribute Encoding

DRP Binary

Encoding

Loading...

Loading...