4200-900-01 Rev. K / February 2017 Return to Section Topics 3-145

Model 4200-SCS User’s Manual Section 3: Common Device Characterization Tests

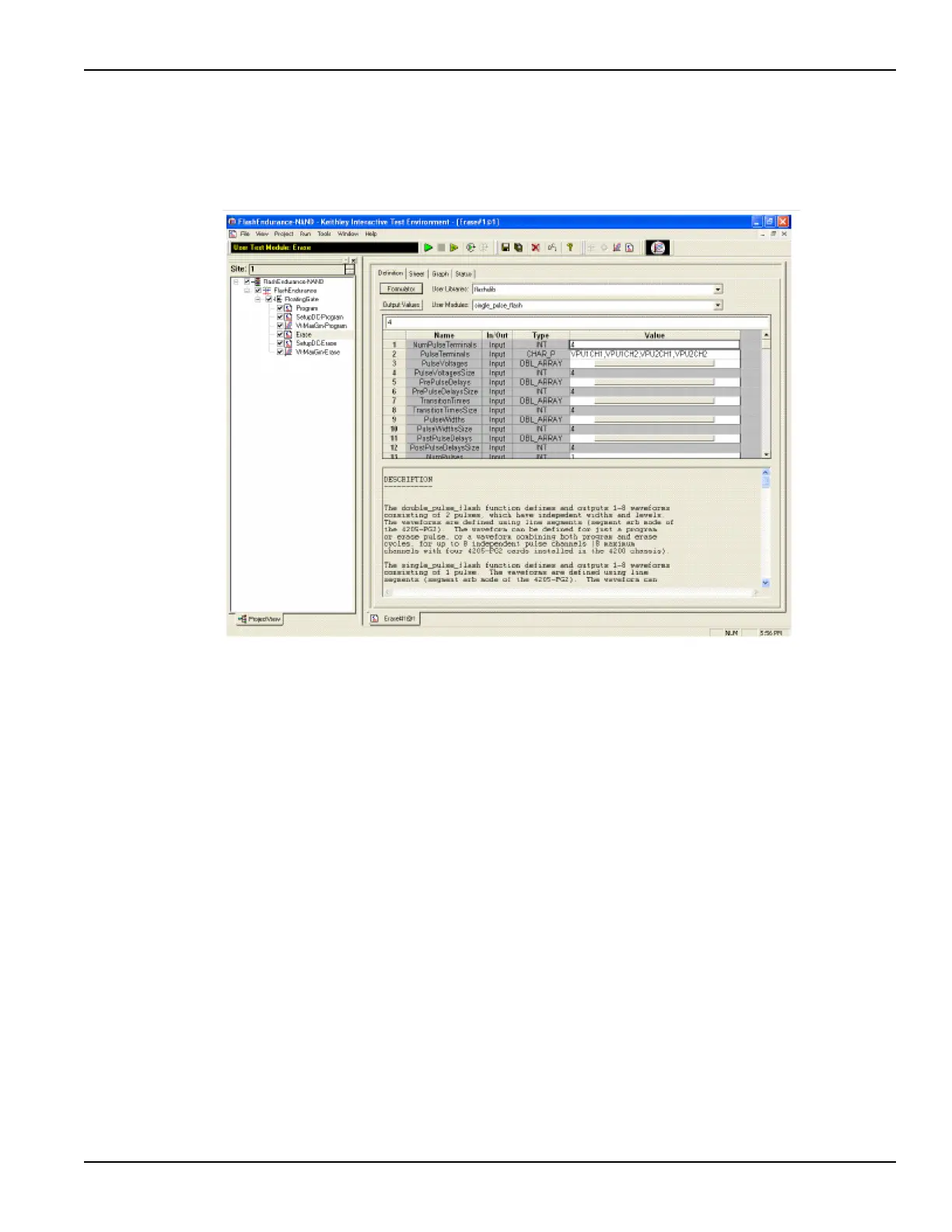

Erase test – This test uses Segment ARB

®

waveforms to program a flash

memory device. The default Definition tab for this test is shown in Figure 3-120.

Figure 3-120

FlashEndurance-NAND project – Erase Definition tab

SetupDC-Erase test – This test isolates the VPU outputs from the DUT. It does

this by opening the HEOR for each VPU channel. Disconnecting the VPU

channels allows for accurate DC results.

Vt-MaxGm-Erase test – This test is used to perform a DC voltage sweep on the

gate of the DUT and measure the drain current at each sweep step. SMU3 is

configured to perform a 101 point sweep from 0 to 5 V in 50 mV steps. SMU1 is

configured to DC bias the drain at 0.5 V and measure current at each step of the

sweep.

The Vt-MaxGm tests may be replaced with another Vt or DC test. Or, additional

DC tests may be added after this test.

FlashEndurance-NOR tests

The FlashEndurance-NOR project has tests similar to the FlashEndurance-NAND

project, with defaults for NOR type floating gate DUTs.

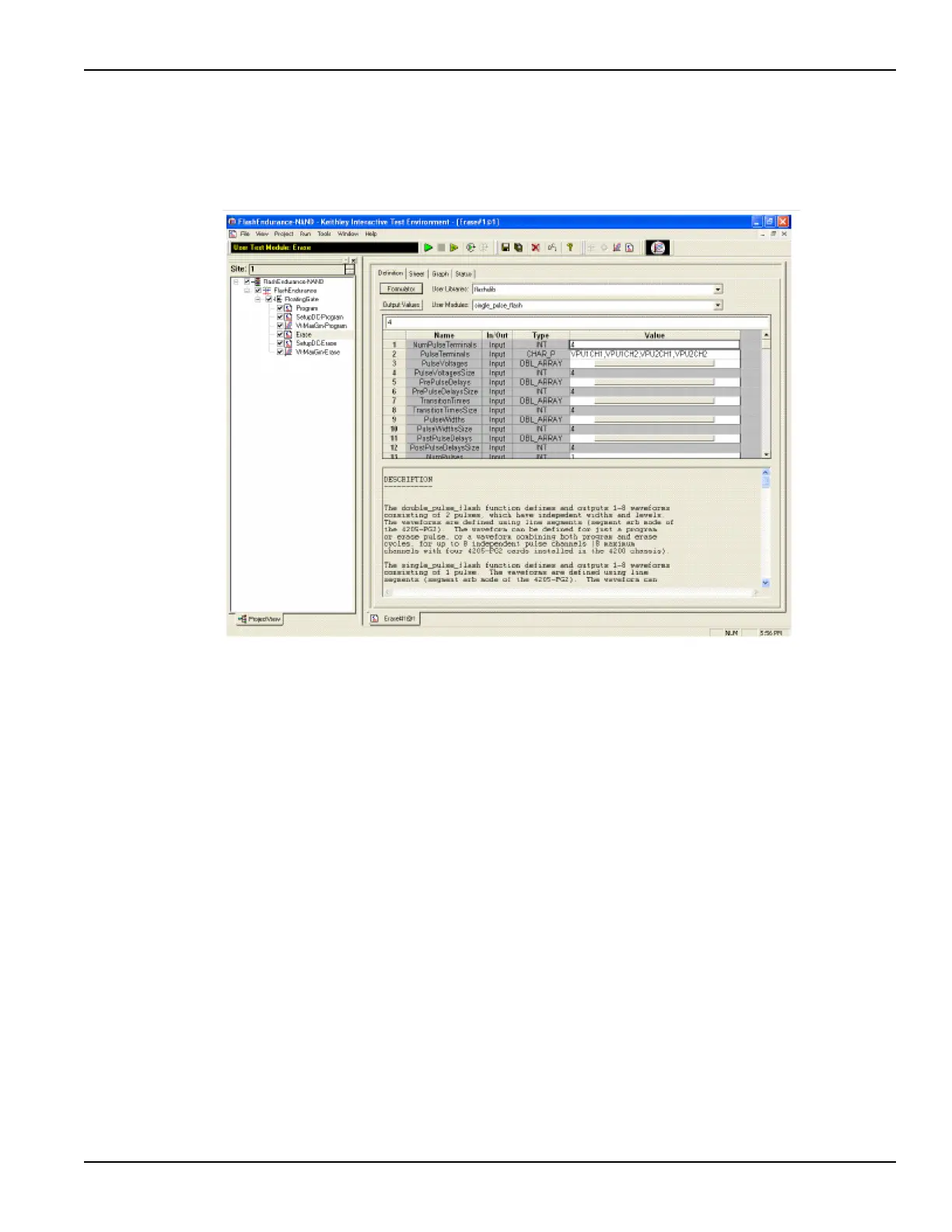

FlashEndurance-switch tests

The FlashEndurance-switch project, Figure 3-121, has similar tests to the

FlashEndurance-NAND, with defaults for using a switch matrix for more complex

multi-DUT addressable test structures (see Figure 3-97). Also note the additional

test, Open-VPU-Relay, added prior to Conpin-DC tests. This step ensures that

Loading...

Loading...