UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 453 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

• angle brackets, <>, enclose alternative forms of the operand

• braces, {}, enclose optional operands and mnemonic parts

• the Operands column is not exhaustive.

For more information on the instructions and operands, see the instruction descriptions.

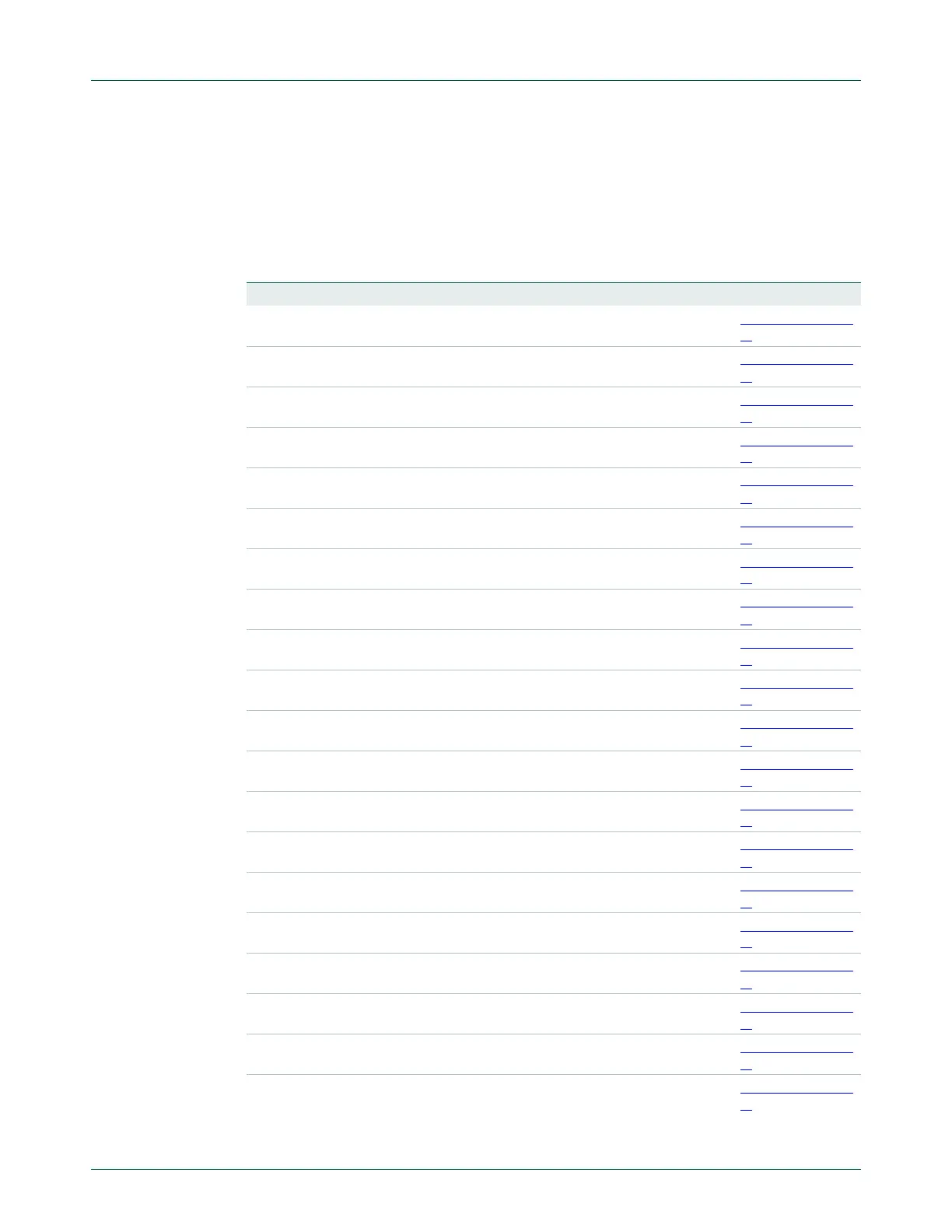

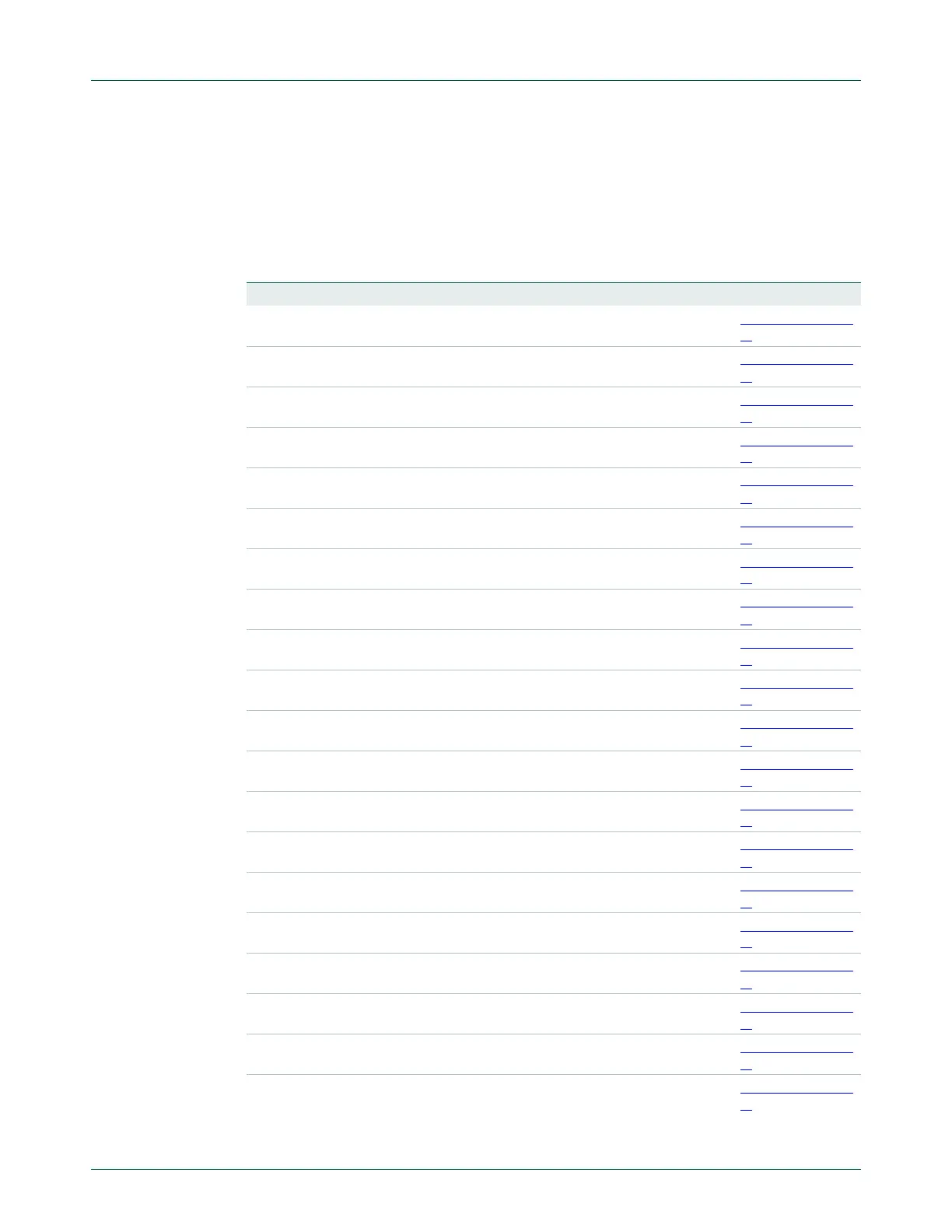

Table 423. Cortex-M0 instructions

Mnemonic Operands Brief description Flags Reference

ADCS {Rd,} Rn, Rm Add with Carry N,Z,C,V Section 24–24.4.5

.1

ADD{S} {Rd,} Rn,

<Rm|#imm>

Add N,Z,C,V Section 24–24.4.5

.1

ADR Rd, label PC-relative Address to Register - Section 24–24.4.4

.1

ANDS {Rd,} Rn, Rm Bitwise AND N,Z Section 24–24.4.5

.1

ASRS {Rd,} Rm, <Rs|#imm> Arithmetic Shift Right N,Z,C Section 24–24.4.5

.3

B{cc} label Branch {conditionally} - Section 24–24.4.6

.1

BICS {Rd,} Rn, Rm Bit Clear N,Z Section 24–24.4.5

.2

BKPT #imm Breakpoint - Section 24–24.4.7

.1

BL label Branch with Link - Section 24–24.4.6

.1

BLX Rm Branch indirect with Link - Section 24–24.4.6

.1

BX Rm Branch indirect - Section 24–24.4.6

.1

CMN Rn, Rm Compare Negative N,Z,C,V Section 24–24.4.5

.4

CMP Rn, <Rm|#imm> Compare N,Z,C,V Section 24–24.4.5

.4

CPSID i Change Processor State,

Disable Interrupts

- Section 24–24.4.7

.2

CPSIE i Change Processor State,

Enable Interrupts

- Section 24–24.4.7

.2

DMB - Data Memory Barrier - Section 24–24.4.7

.3

DSB - Data Synchronization Barrier - Section 24–24.4.7

.4

EORS {Rd,} Rn, Rm Exclusive OR N,Z Section 24–24.4.5

.2

ISB - Instruction Synchronization

Barrier

- Section 24–24.4.7

.5

LDM Rn{!}, reglist Load Multiple registers,

increment after

- Section 24–24.4.4

.5

Loading...

Loading...