Program instructions

7.6 Counters

S7-200 SMART

238 System Manual, 09/2015, A5E03822230-AC

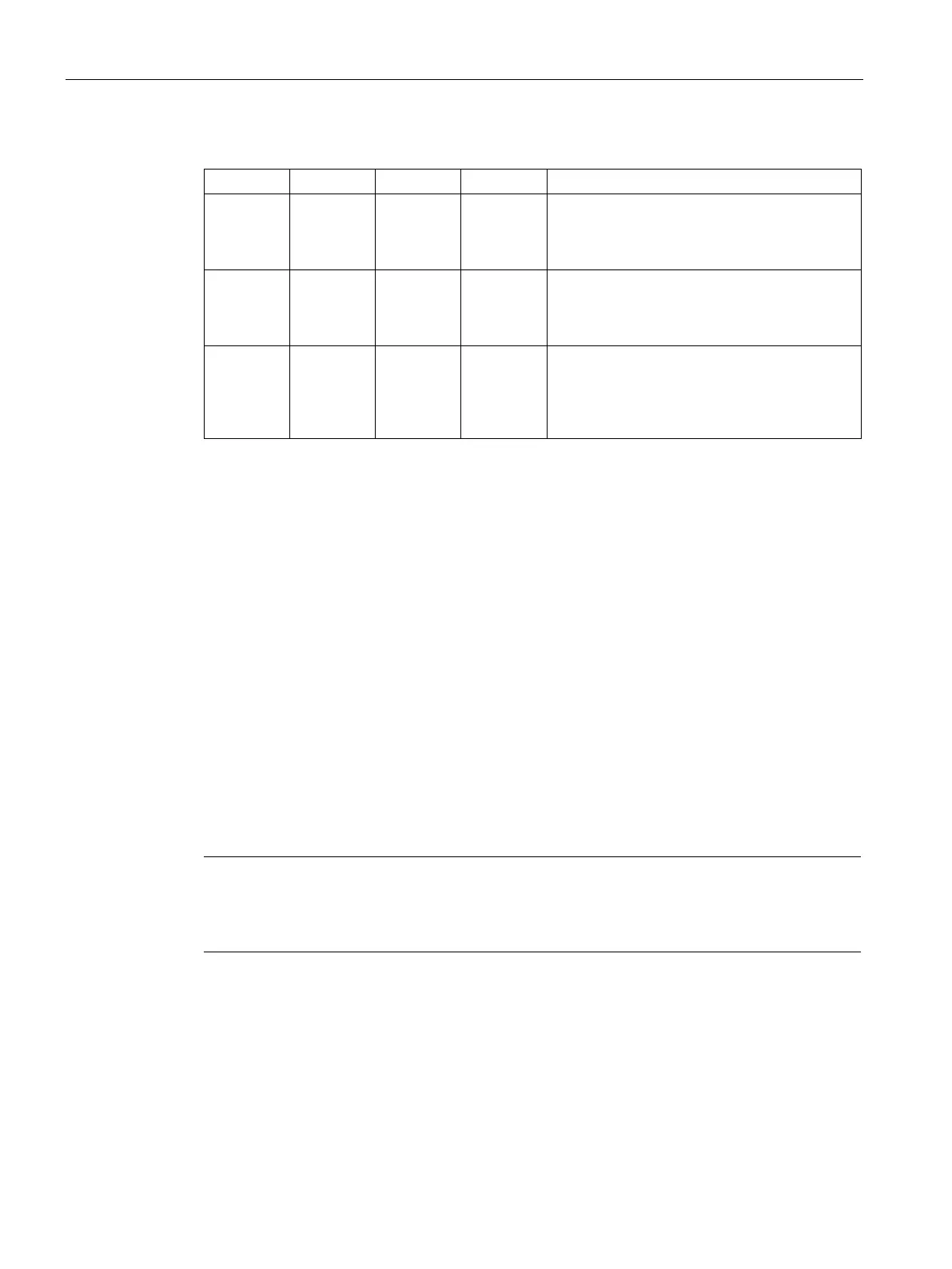

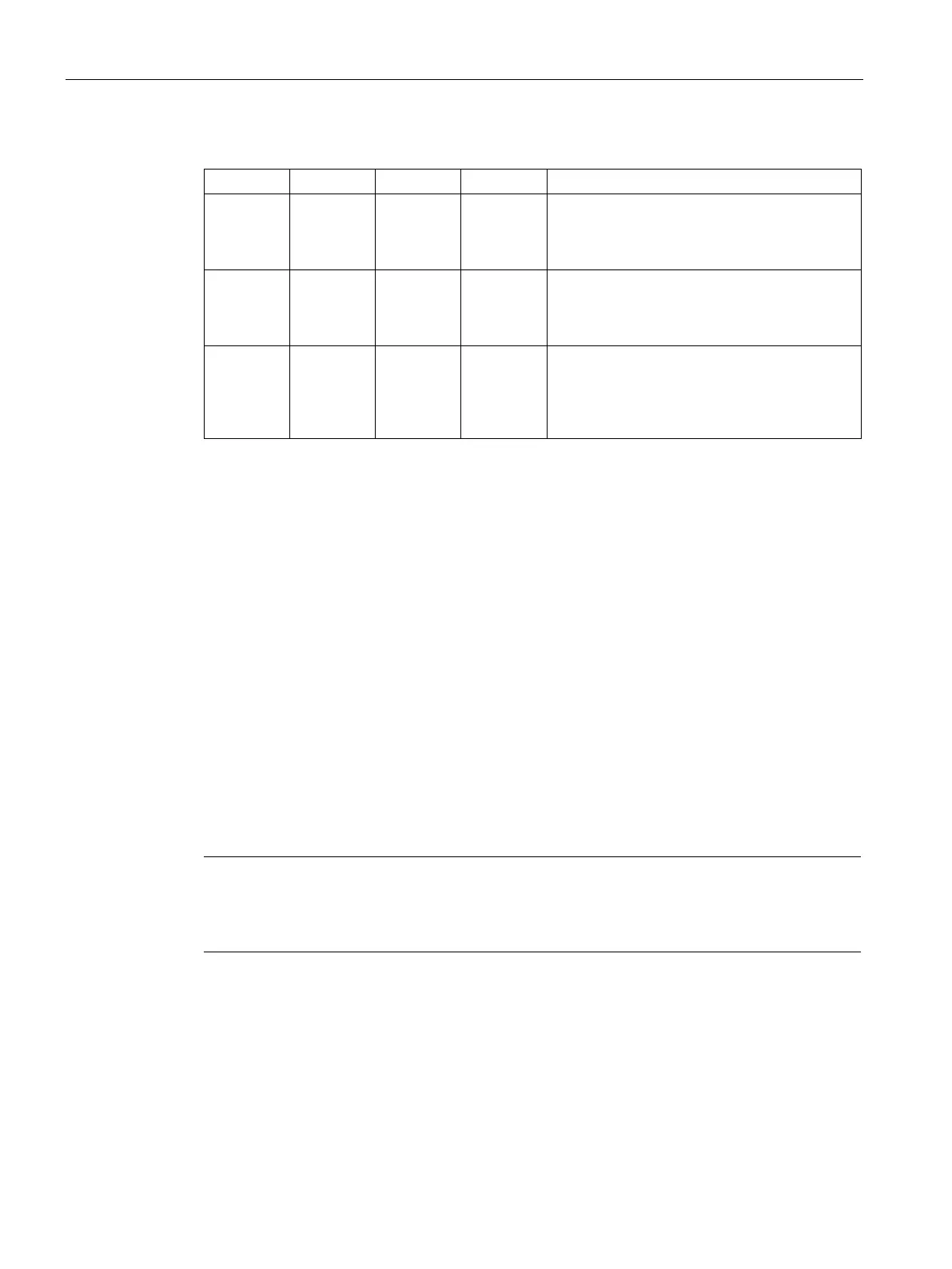

Table 7- 7 Status bits for HSC0, HSC1, HSC2, and HSC3

SM36.5 SM46.5 SM56.5 SM136.5

Current counting direction status bit:

• 0 = Counting down

• 1 = Counting up

SM36.6 SM46.6 SM56.6 SM136.6

Current value equals preset value status bit:

• 0 = Not equal

• 1 = Equal

SM36.7 SM46.7 SM56.7 SM136.7

Current value greater than preset value status

bit:

• 0 = Less than or equal

• 1 = Greater than

High-speed counter instructions (Page 220)

Example initialization sequences for the high-speed counters (Page 238)

Example initialization sequences for high-speed counters

HSC0 is used as the counter in the following descriptions of the initialization and operation

sequences.

● HSC0 and HSC2 support counting modes (0, 1), (3, 4), (6, 7), and (9, 10).

● HSC1 and HSC3 only support counting mode 0.

The initialization descriptions assume that the CPU has just been placed in RUN mode, and

for that reason, the first scan memory bit is true. If this is not the case, remember that the

HDEF instruction can be executed only one time for each high-speed counter, after entering

RUN mode. Executing HDEF for a high-speed counter a second time generates a run-time

error and does not change the counter setup from the way it was set up on the first execution

of HDEF for that counter.

Note

Although the following sequences show how to change direction, current value, and preset

value individually, you can change all or any combination of them in the same sequence by

setting the value of SM

B37 appropriately and then executing the HSC instruction.

Loading...

Loading...