Program instructions

7.6 Counters

S7-200 SMART

224 System Manual, 09/2015, A5E03822230-AC

Noise reduction for high-speed inputs

Counting high-speed pulses with HSC inputs

Note

High-speed input wiring must use shielded cables

Use shielded cable with a maximum length of 50 m, when connecting HSC input channels

I0.0, I0.1, I0.2, and I0.3.

One or both of the following actions may be necessary to correctly operate a high-speed

counter.

● Adjust the System Block digital input filter time of the input channels used by the HSC

channel. In an S7-200 SMART CPU. Input filtering is applied before the counting of

pulses by the HSC channel. This means that if an HSC input pulse occurs at a rate that is

filtered out by the input filtering, then the HSC does not detect any pulses on the input.

You must make sure that you configure the filter time of each input of the HSC to a value

that will allow counting at the rate your application requires. This includes direction and

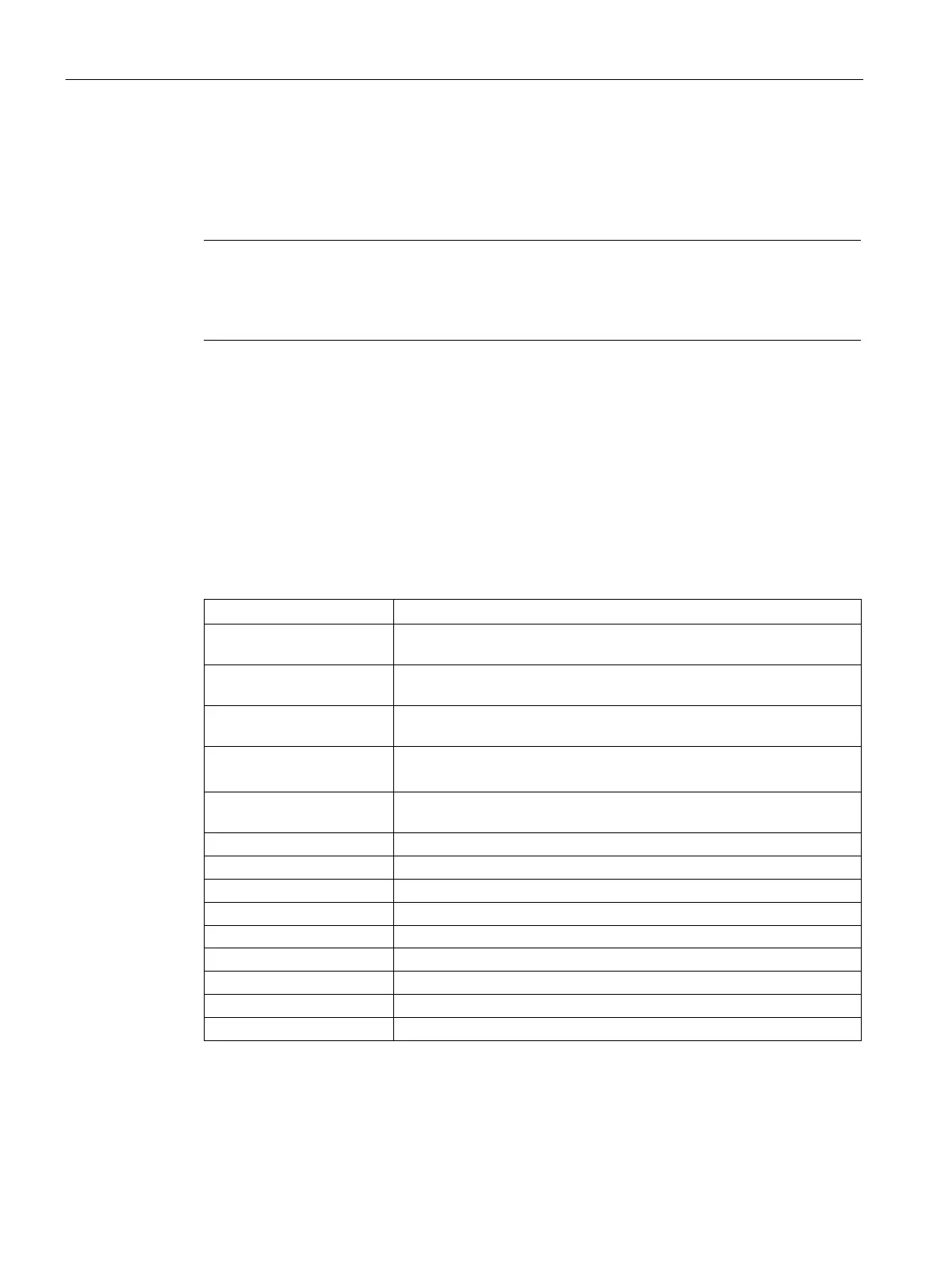

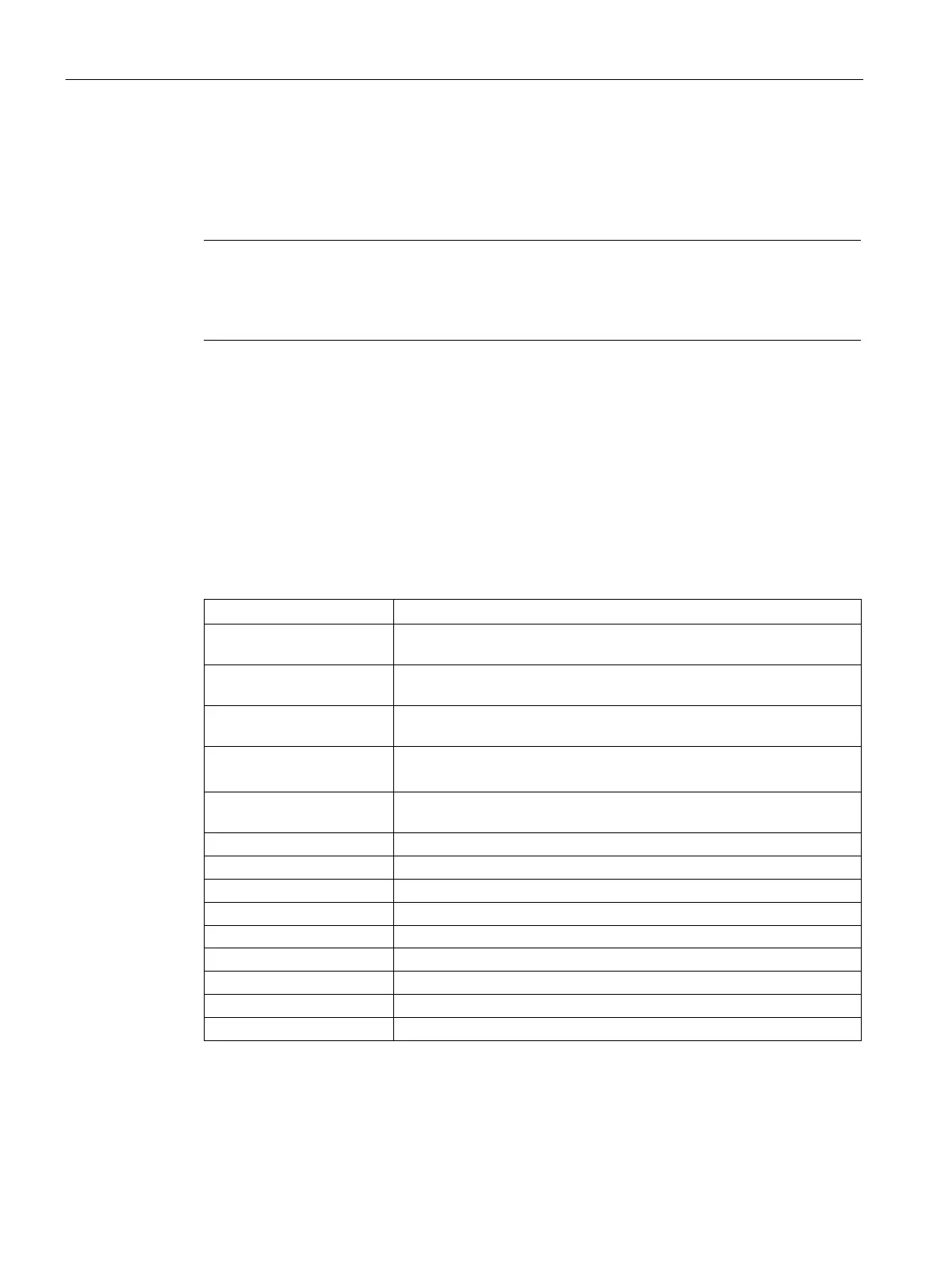

reset inputs. The following table shows the maximum input frequency that can be

detected for each input filter configuration.

Maximum detectable frequency

0.2 μs 200 kHz for S model CPUs

1

2

0.4 μs 200 kHz for S model CPUs

0.8 μs 200 kHz for S model CPUs

1.6 μs 200 kHz for S model CPUs

3.2 μs 156 kHz for S model CPUs

0.2 ms 2.5 kHz

0.8 ms 625 Hz

S model CPUs: SR20, ST20, SR30, ST30, SR40, ST40, SR60, ST60

2

C model CPUs: CR40, CR60

Loading...

Loading...