Technical specifications

A.2 S7-200 SMART CPUs

S7-200 SMART

594 System Manual, 09/2015, A5E03822230-AC

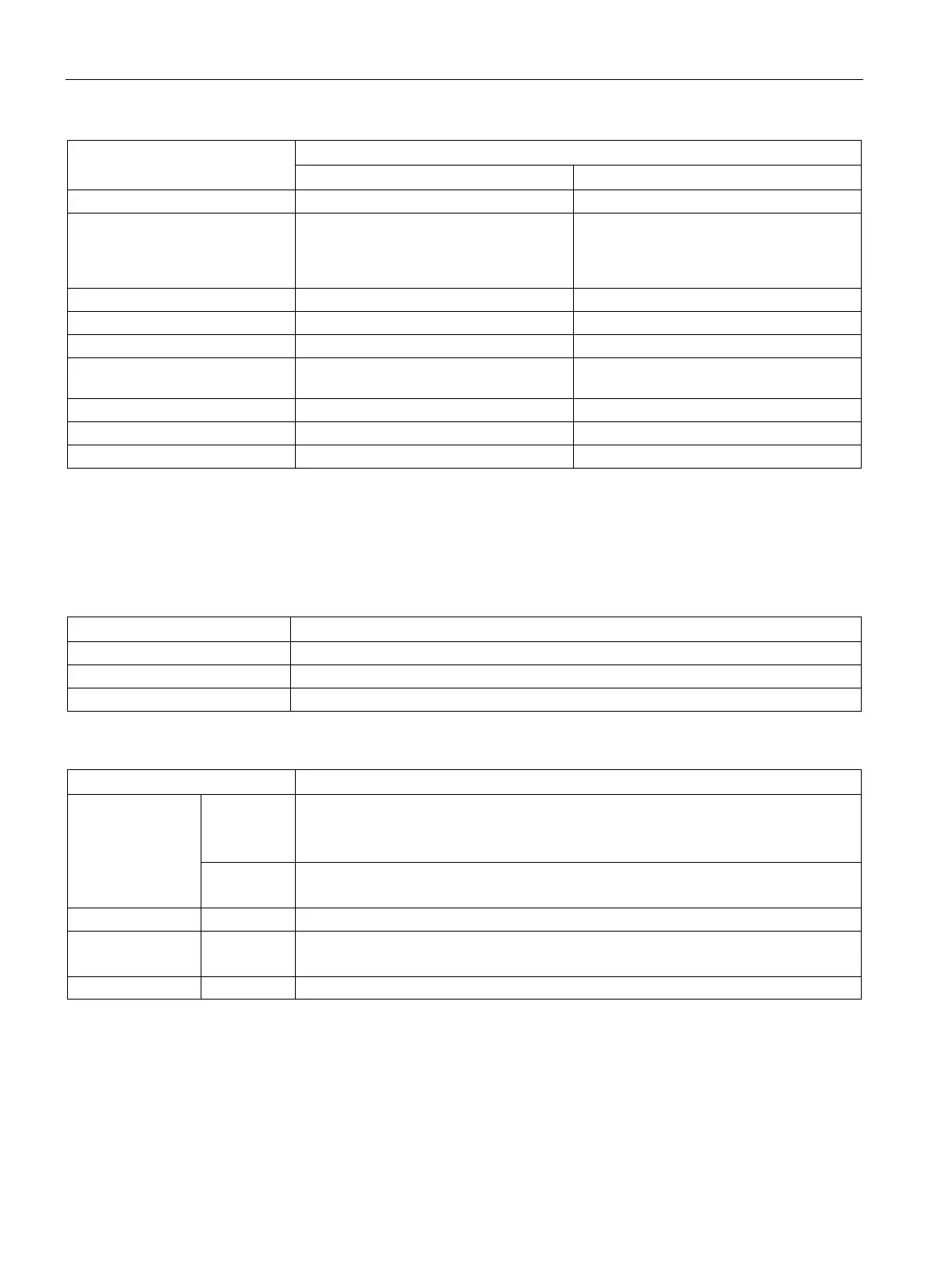

High-speed counters 4 total

• 4 at 200 KHz single phase

• 2 at 100 KHz A/B phase

4 total

• 4 at 100 KHz single phase

• 2 at 50 KHz A/B phase

Pulse outputs

2

3 at 100 KHz --

Cyclic interrupts 2 at 1 ms resolution 2 at 1 ms resolution

Edge interrupts 4 rising and 4 falling (6 and 6 with option-

4 rising and 4 falling

microSDHC card (optional)

microSDHC card (optional)

Real time clock retention time

7 days typ./6 days min. at 25°C

You can configure areas of V memory, M memory, C memory (current values) and portions of T memory (current values

on retentive timers) to be retentive, up to the specified maximum amount.

The specified maximum pulse frequency is possible only for CPU models with transistor outputs. Pulse output operation

is not recommended for CPU models with relay outputs.

Table A- 51 Performance

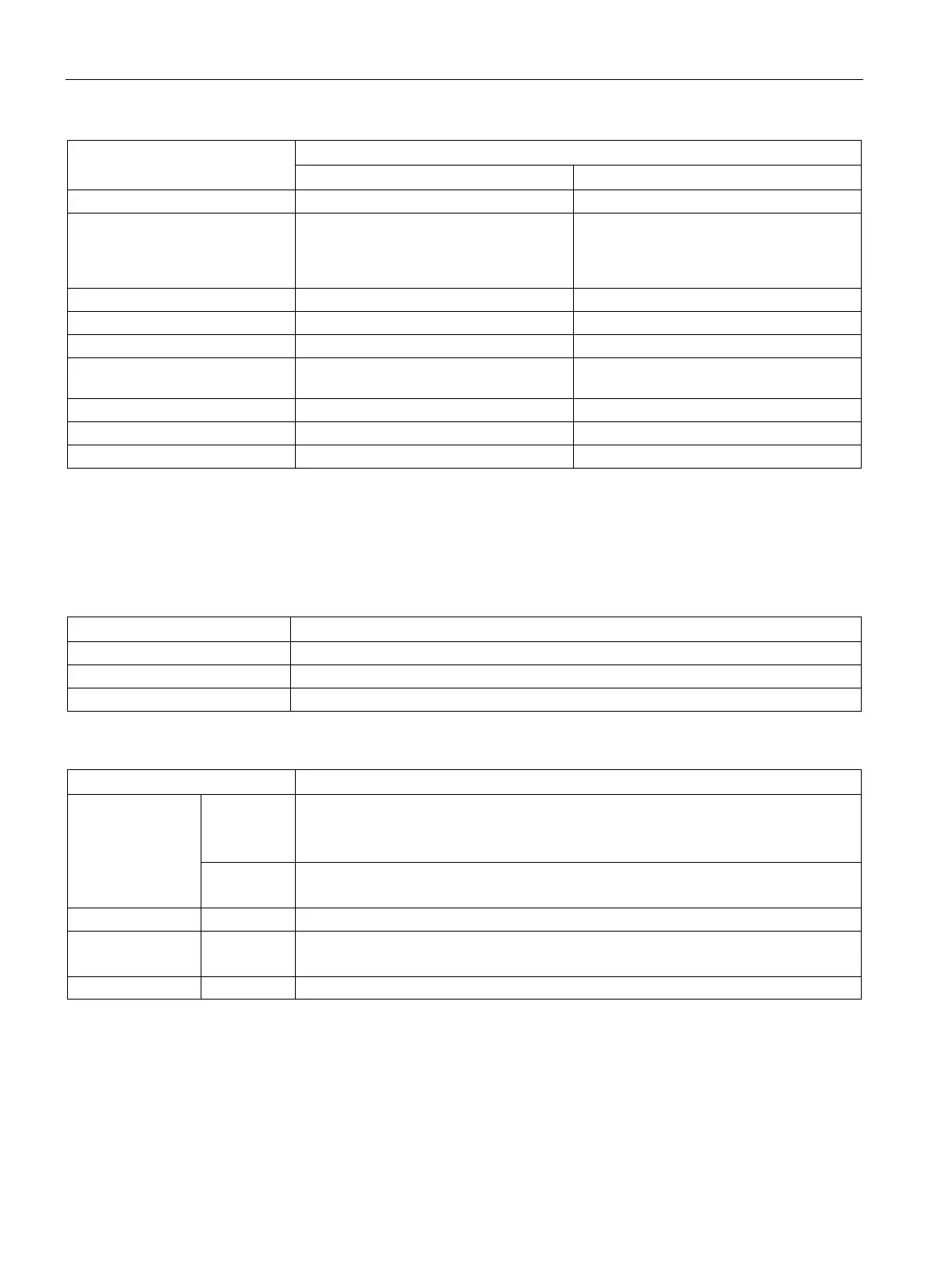

Table A- 52 User program elements supported

POUs Type/ quan-

tity

Main program: 1

Subroutines: 128 (0 to 127)

Interrupt routines: 128 (0 to 127)

Nesting

depth

From main program: 8 subroutine levels

From interrupt routine: 4 subroutine levels

Timers Type/ quan-

tity

Non-retentive (TON, TOF): 192

Counters Quantity 256

Loading...

Loading...