GD32VF103 User Manual

110

1. For different packages and flash sizes please refer to the datasheet.

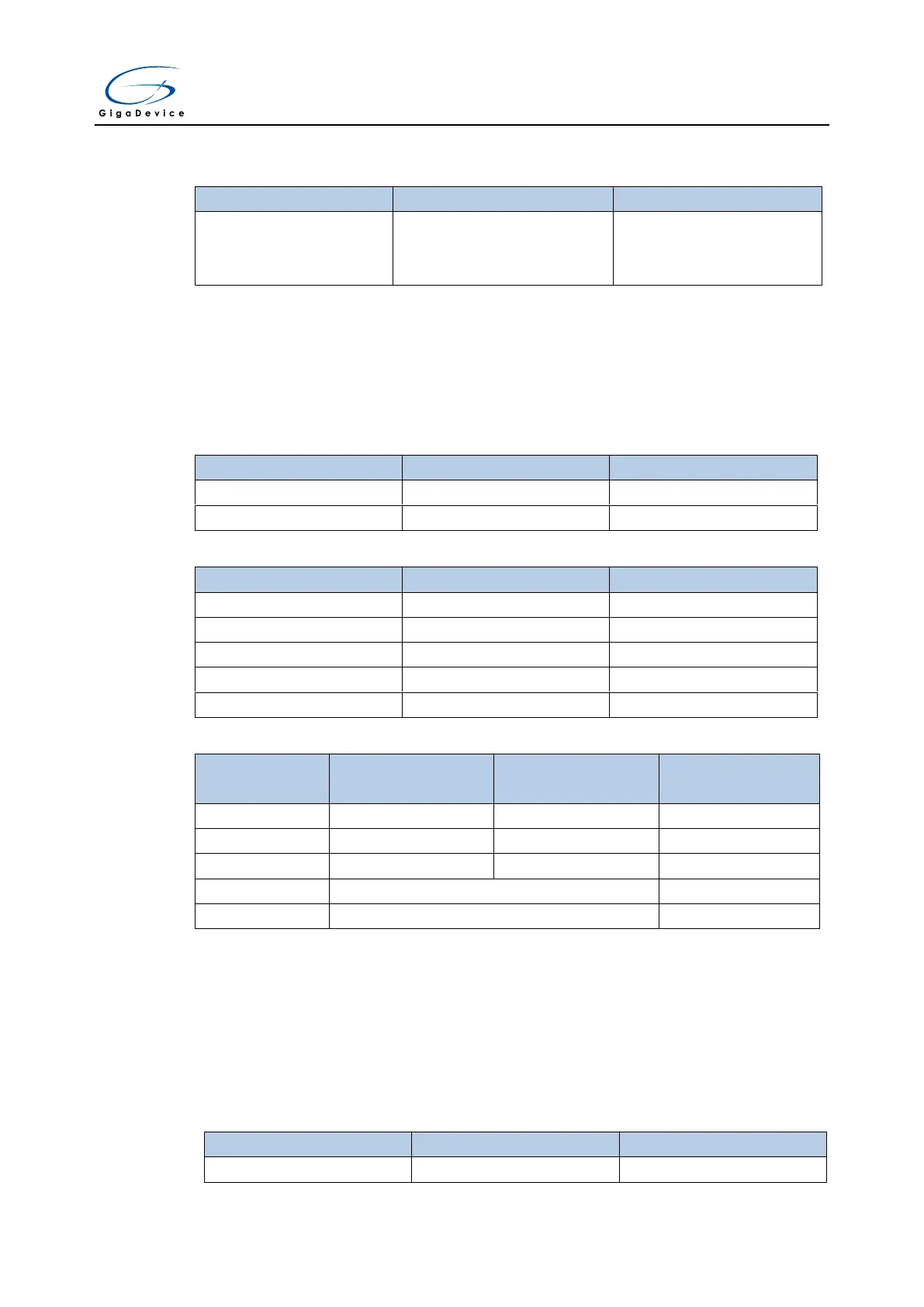

Table 7.8. TIMER4 alternate function remapping

TIMER4_CH3 is connected to PA3

IRC40K internal clock is

connected to TIMER4_CH3

input for calibration purpose

1. For different packages and flash sizes please refer to the datasheet.

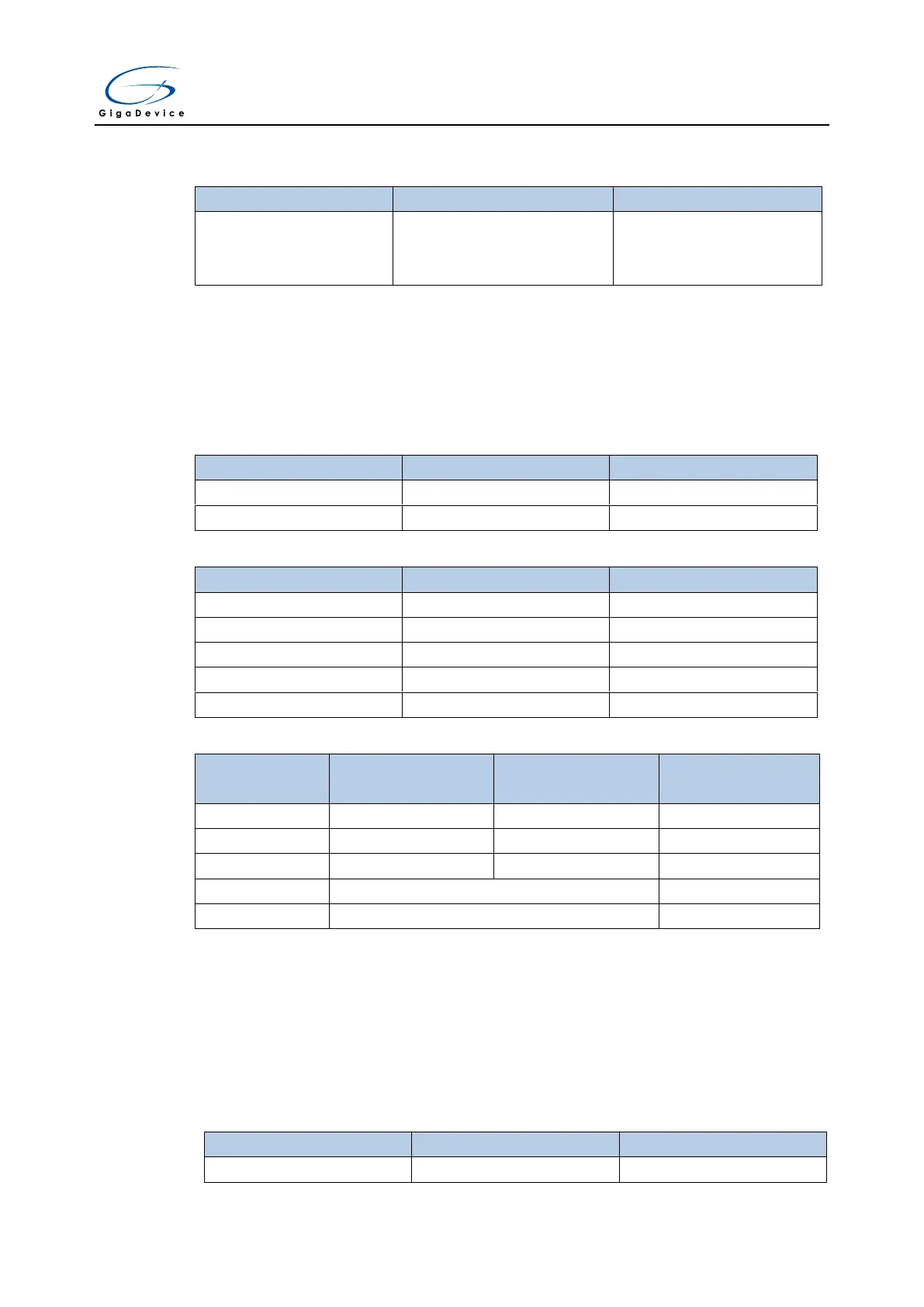

7.4.5. USART AF remapping

Refer to AFIO port configuration register 0 (AFIO_PCF0).

Table 7.9. USART0 alternate function remapping

Table 7.10. USART1 alternate function remapping

Table 7.11. USART2 alternate function remapping

USART2_REMAP [1:0] =

“00” (no remap)

USART2_REMAP [1:0]

=“01” (partial remap)

(1)

USART2_REMAP [1:0]

=“11” (full remap)

(2)

2. Remap available only for 64-pin,100-pin

3. Remap available only 100-pin

7.4.6. I2C0 AF remapping

Refer to AFIO port configuration register 0 (AFIO_ PCF0).

Table 7.12. I2C0 alternate function remapping

Loading...

Loading...