GD32VF103 User Manual

381

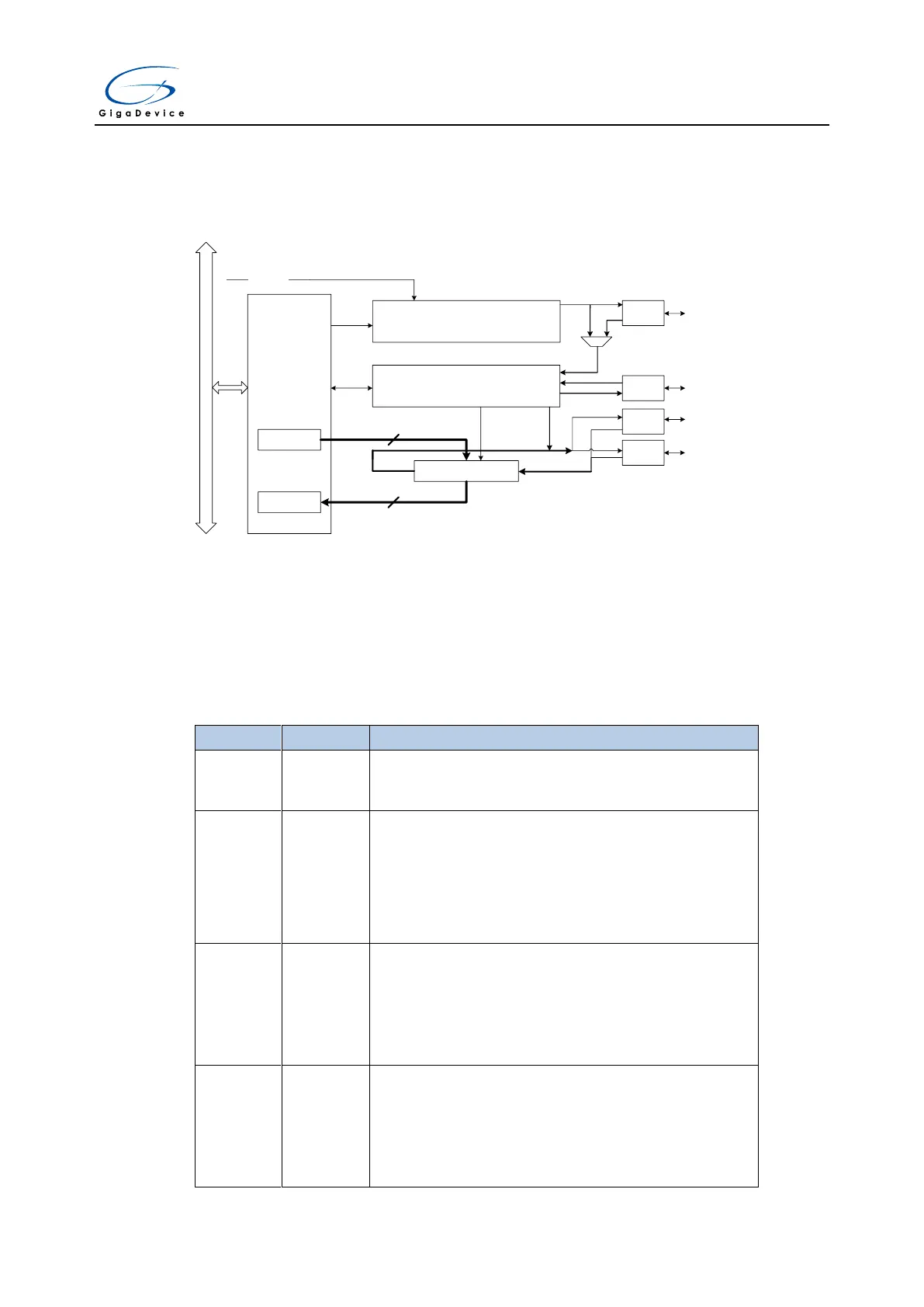

18.3. SPI block diagram

Figure 18-1. Block diagram of SPI

Clock Generator

MISO

NSS

SCK

MOSI

TxRx Control Logic

TX Buffer

Shift Register

RX Buffer

Control

Registers

SYSCLK

LSB

MSB

APB

PAD

O

I

PAD

O

I

PAD

O

I

PAD

O

I

18.4. SPI signal description

18.4.1. Normal configuration

Table 18-1. SPI signal description

Master: Data reception line

Slave: Data transmission line

Master with bidirectional mode: Not used

Slave with bidirectional mode: Data transmission and

reception line.

Master: Data transmission line

Slave: Data reception line

Master with bidirectional mode: Data transmission and

reception line.

Slave with bidirectional mode: Not used

Software NSS mode: Not used

Master in hardware NSS mode: NSS output for single master

(NSSDRV=1) or for multi-master (NSSDRV=0) application.

Slave in hardware NSS mode: NSS input, as a chip select

signal for slave.

Loading...

Loading...