GD32VF103 User Manual

231

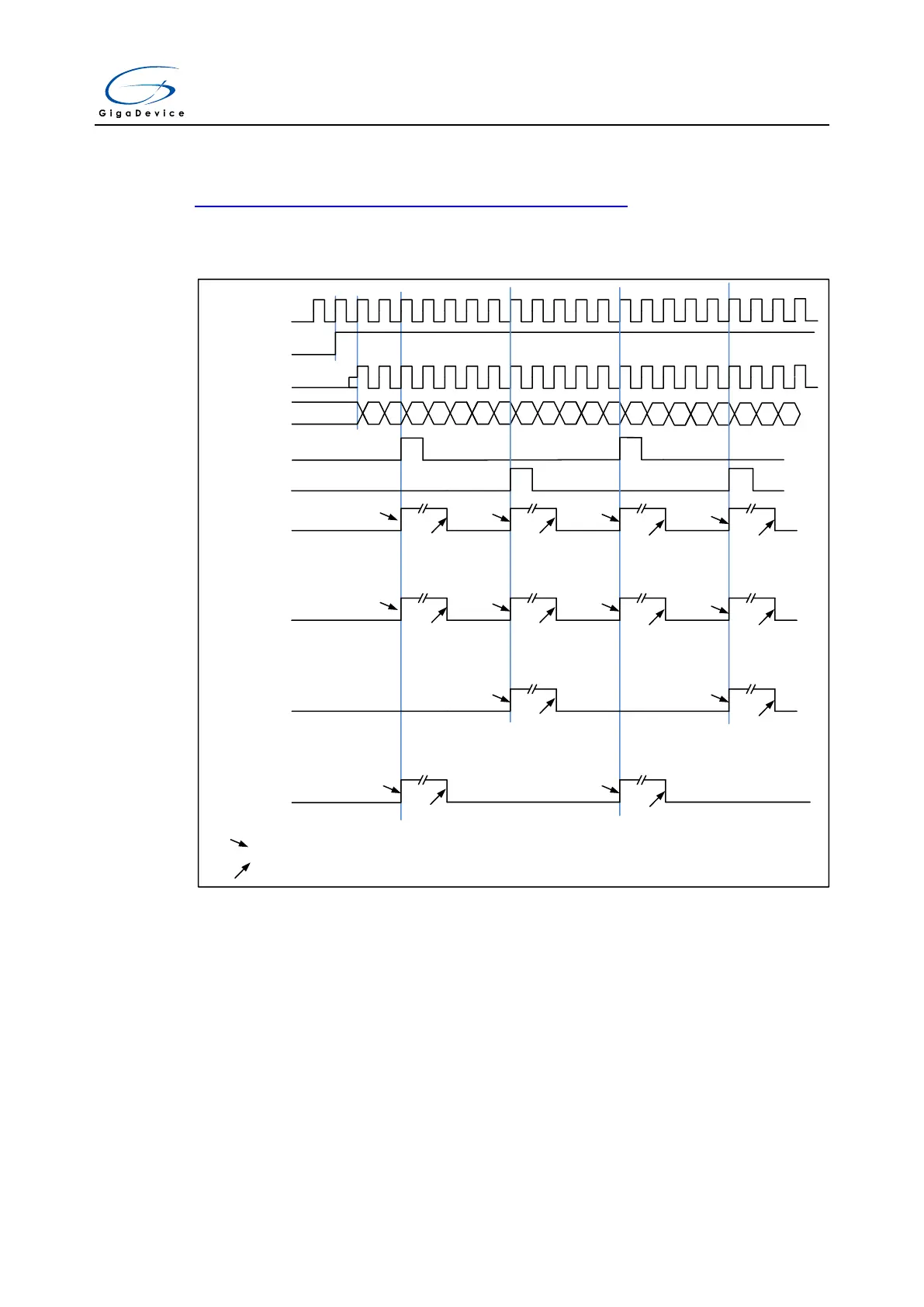

When an update event occurs, all the registers (repetition counter register, auto-reload

register, prescaler register) are updated.

Figure 15-8. Timing chart of center-aligned counting mode show some examples of the

counter behavior when TIMERx_CAR=0x63. TIMERx_PSC=0x0

Figure 15-8. Timing chart of center-aligned counting mode

Hardware set

Software clear

CEN

CNT_CLK

(PSC_CLK)

CNT_REG

03 02 01 00 01 02

….

62 63 62 61

….

01 00

Underflow

Overflow

TIMERx_CTL0 CAM = 2'b11

TIMER_CK

01

02

….

62 63 62

61

UPIF

CHxIF

CHxIF

TIMERx_CTL0 CAM = 2'b10 (upcount only )

TIMERx_CTL0 CAM = 2'b10 (downcount only )

CHxIF

Repetition counter

Repetition counter is used to generate the update event or update the timer registers only

after a given number (N+1) cycles of the counter, where N is the value of CREP bit in

TIMERx_CREP register. The repetition counter is decremented at each counter overflow in

up counting mode, at each counter underflow in down counting mode or at each counter

overflow and at each counter underflow in center-aligned mode.

Setting the UPG bit in the TIMERx_SWEVG register will reload the content of CREP in

TIMERx_CREP register and generate an update event.

Loading...

Loading...