GD32VF103 User Manual

293

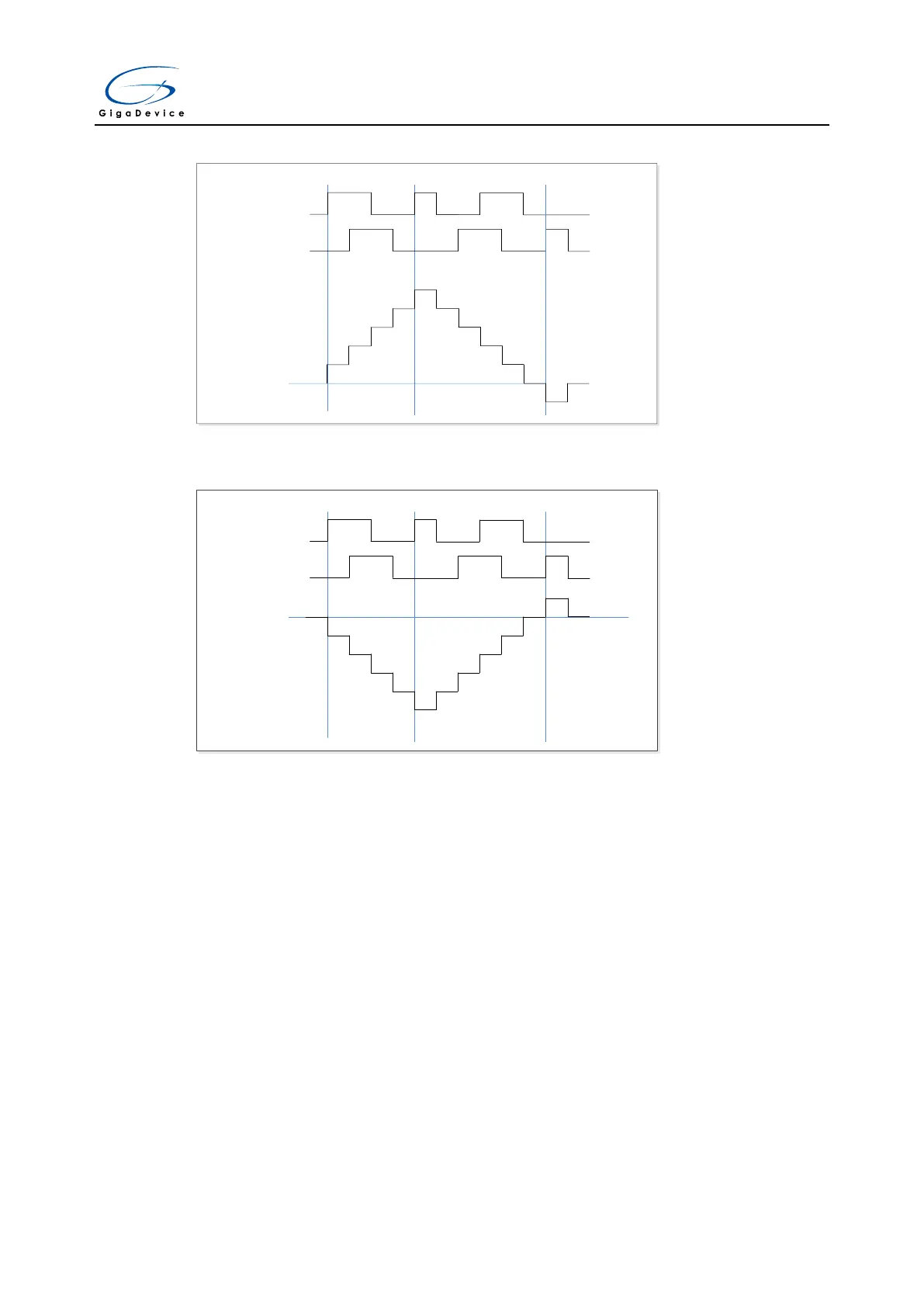

Figure 15-46. Example of counter operation in encoder interface mode

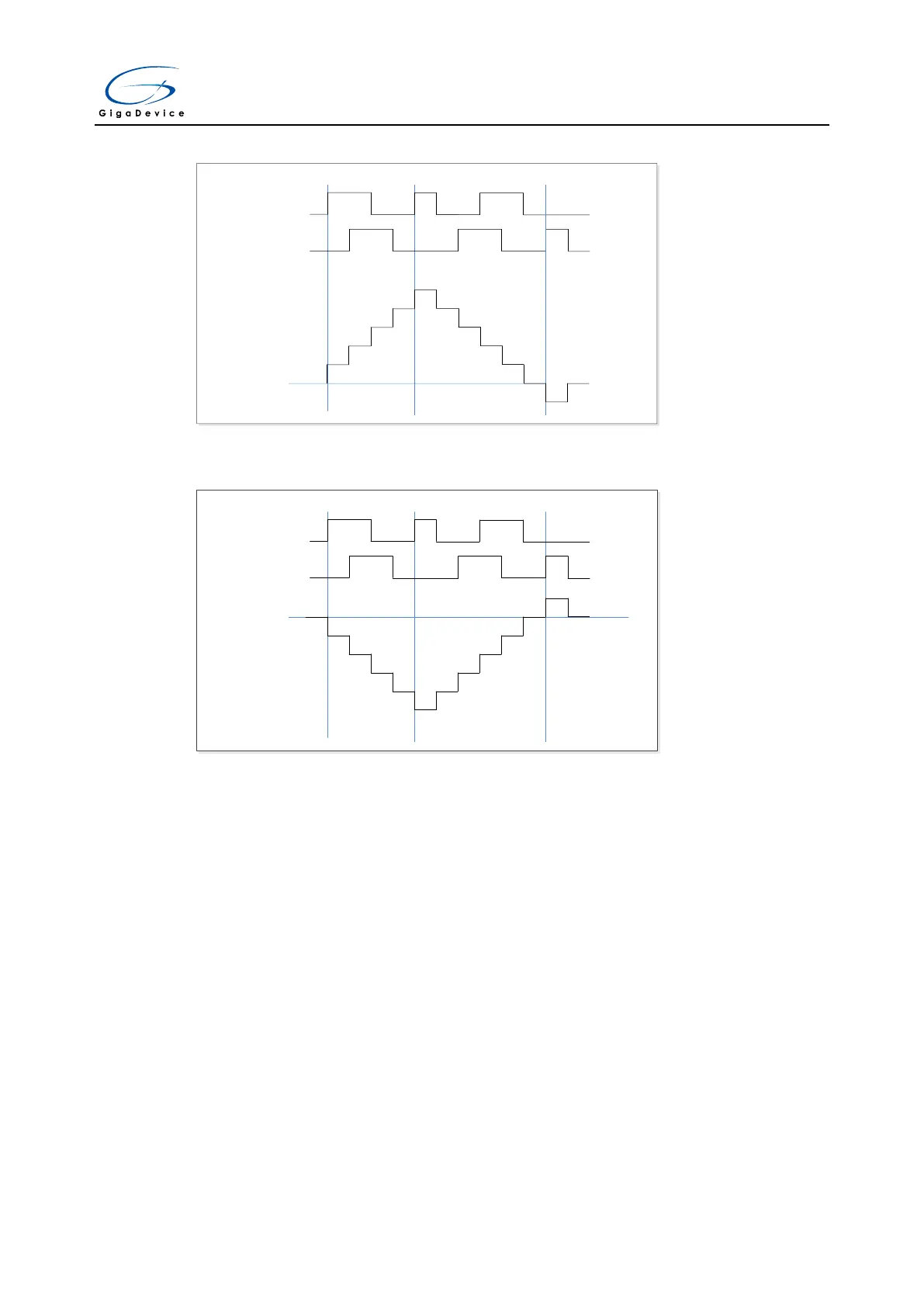

Figure 15-47. Example of encoder interface mode with CI0FE0 polarity inverted

Hall sensor function

Refer to Advanced timer (TIMERx, x=0).

Slave controller

The TIMERx can be synchronized with a trigger in several modes including restart mode,

pause mode and event mode which is selected by the SMC[2:0] bits in the TIMERx_SMCFG

register. The input trigger of these modes can be selected by the TRGS[2:0] bits in the

TIMERx_SMCFG register.

Loading...

Loading...