GD32VF103 User Manual

421

Table 19-5. EXMC_timing models

NOR Flash address/data mux

As shown in Table 19-5. EXMC_timing models, EXMC NOR Flash / PSRAM controller

provides a timing model, users can modify those parameters listed in Table 19-4. NOR /

PSRAM controller timing parameters to satisfy different external memory type and user’s

requirements. Different timing patterns for read and write access could be generated

independently according to EXMC_SNTCFGx register’s configuration.

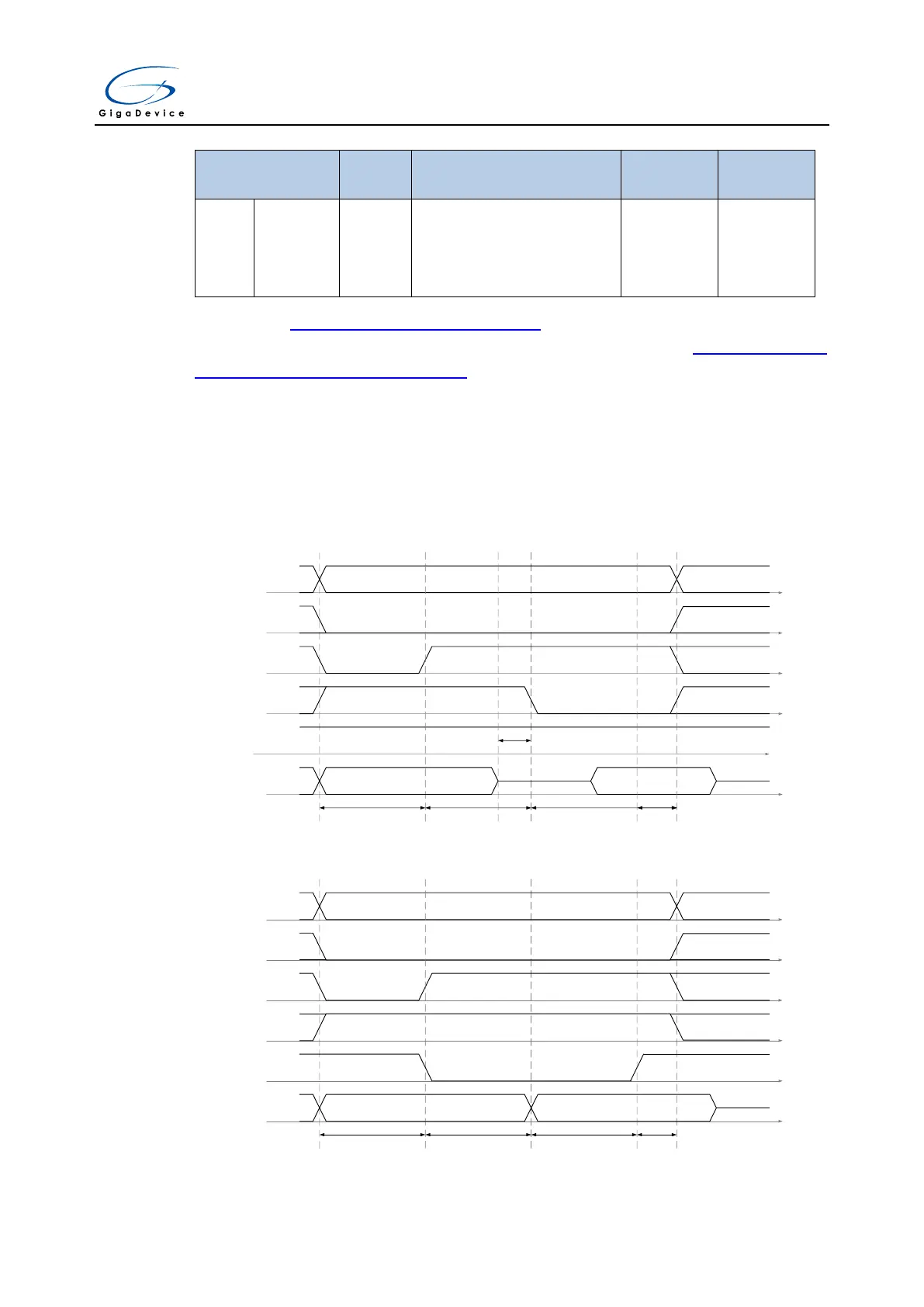

Asynchronous access timing diagram

Mode AM - NOR Flash address / data bus multiplexing

Figure 19-4. Multiplex mode read access

1 HCLK

Address

(EXMC_A[25:16])

Address Valid

(EXMC_NADV)

Chip Enable

(EXMC_NEx)

Output Enable

(EXMC_NOE)

Write Enable

(EXMC_NWE)

Data Mux

(EXMC_D[15:0])

Memory Output

Address Setup Time

(ASET+1 HCLK)

Data Setup Time

(DSET+1 HCLK)

Address Hold Time

(AHLD+1 HCLK)

Address[15:0]

Address[25:16]

2 HCLK

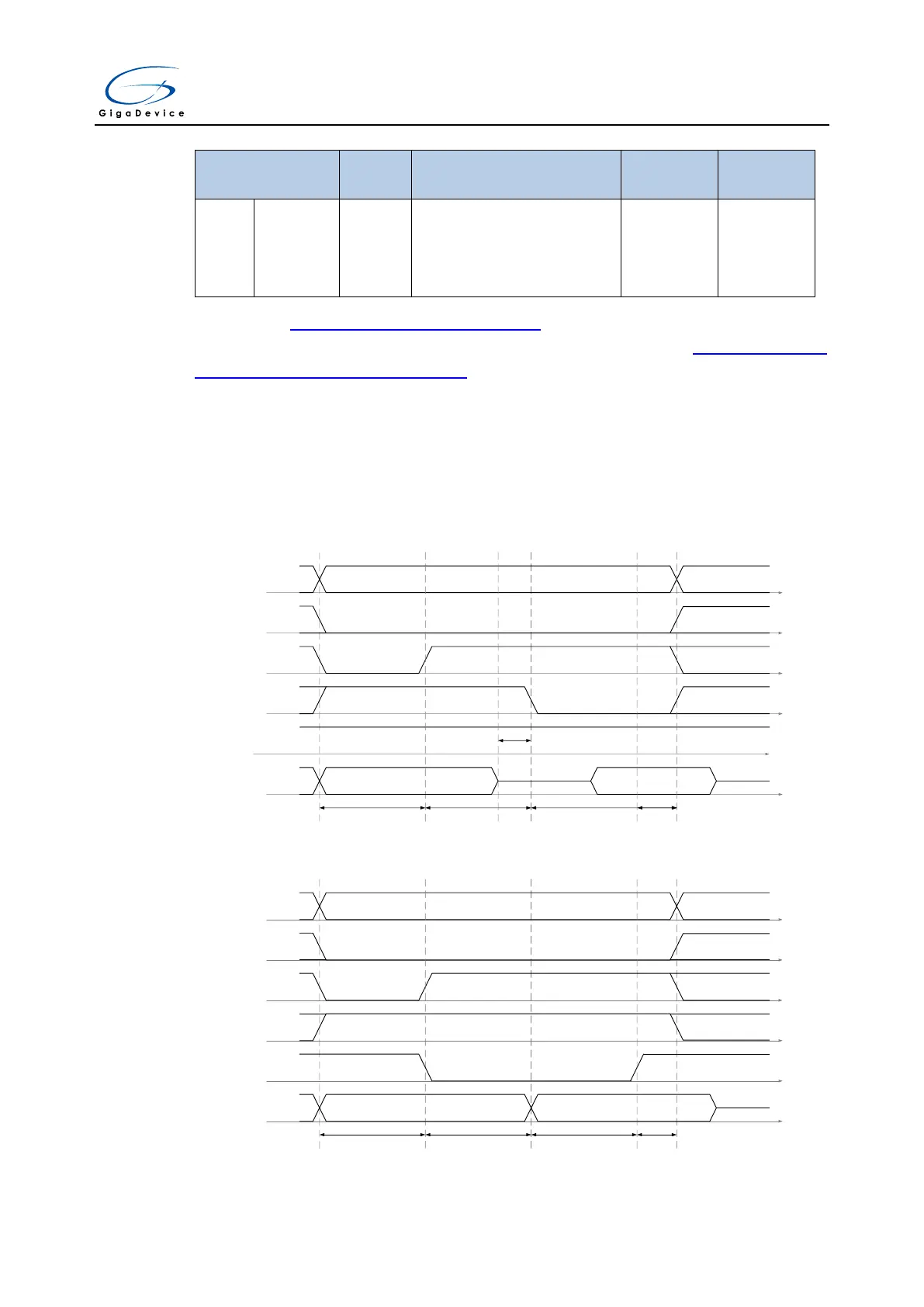

Figure 19-5. Multiplex mode write access

Address

(EXMC_A[25:16])

Address Valid

(EXMC_NADV)

Chip Enable

(EXMC_NEx)

Output Enable

(EXMC_NOE)

Write Enable

(EXMC_NWE)

Data

(EXMC_D[15:0])

Address Setup Time

(ASET+1 HCLK)

Data Setup Time

(DSET+1 HCLK)

1 HCLK

Address Hold Time

(AHLD HCLK)

Address[15:0]

Address[25:16]

EXMC output

Loading...

Loading...