GD32VF103 User Manual

150

10.4. Register definition

DBG base address: 0xE004 2000

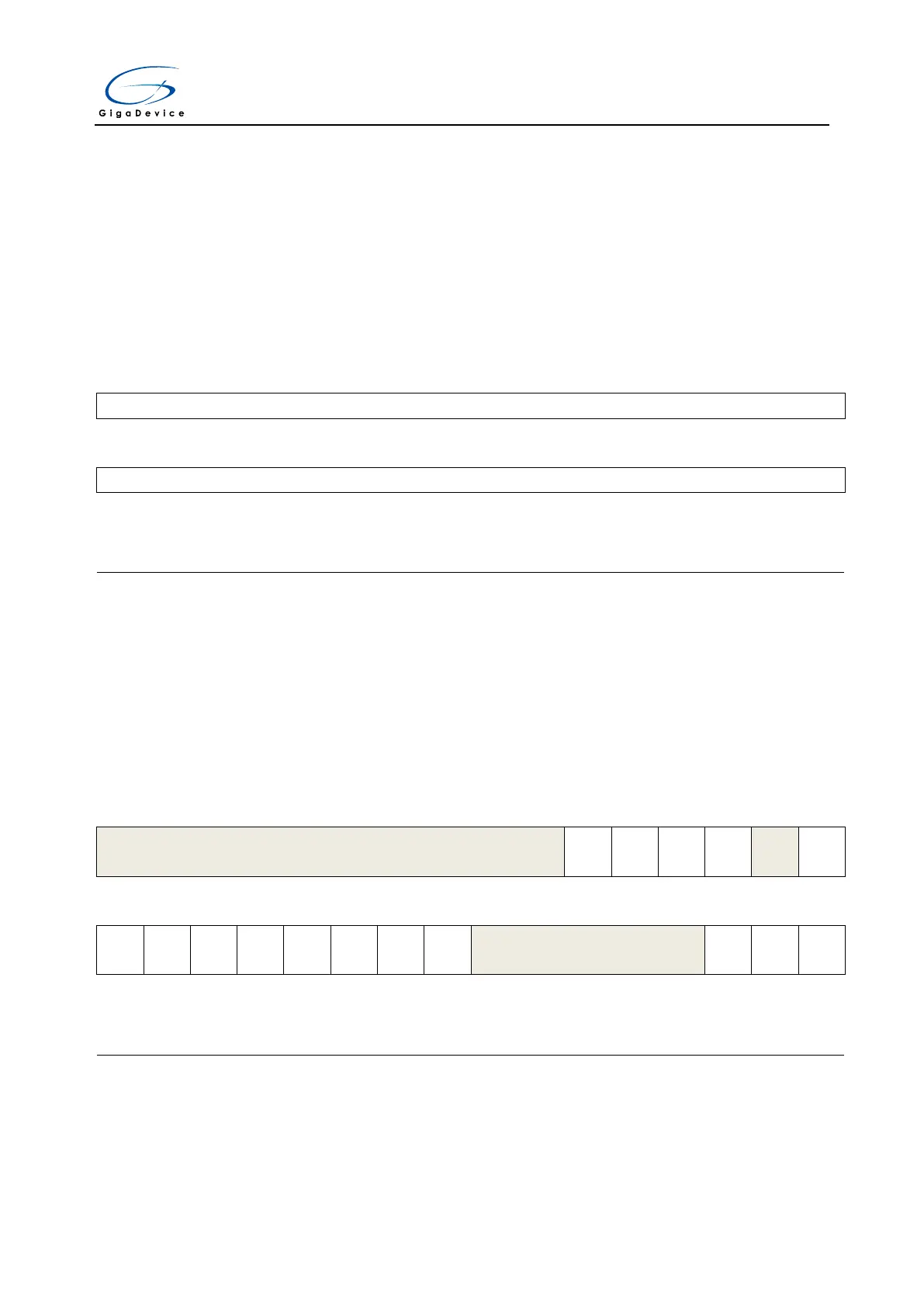

10.4.1. ID code register (DBG_ID)

Address: 0xE004 2000

Read only

This register has to be accessed by word(32-bit)

These bits read by software, These bits are unchanged constant

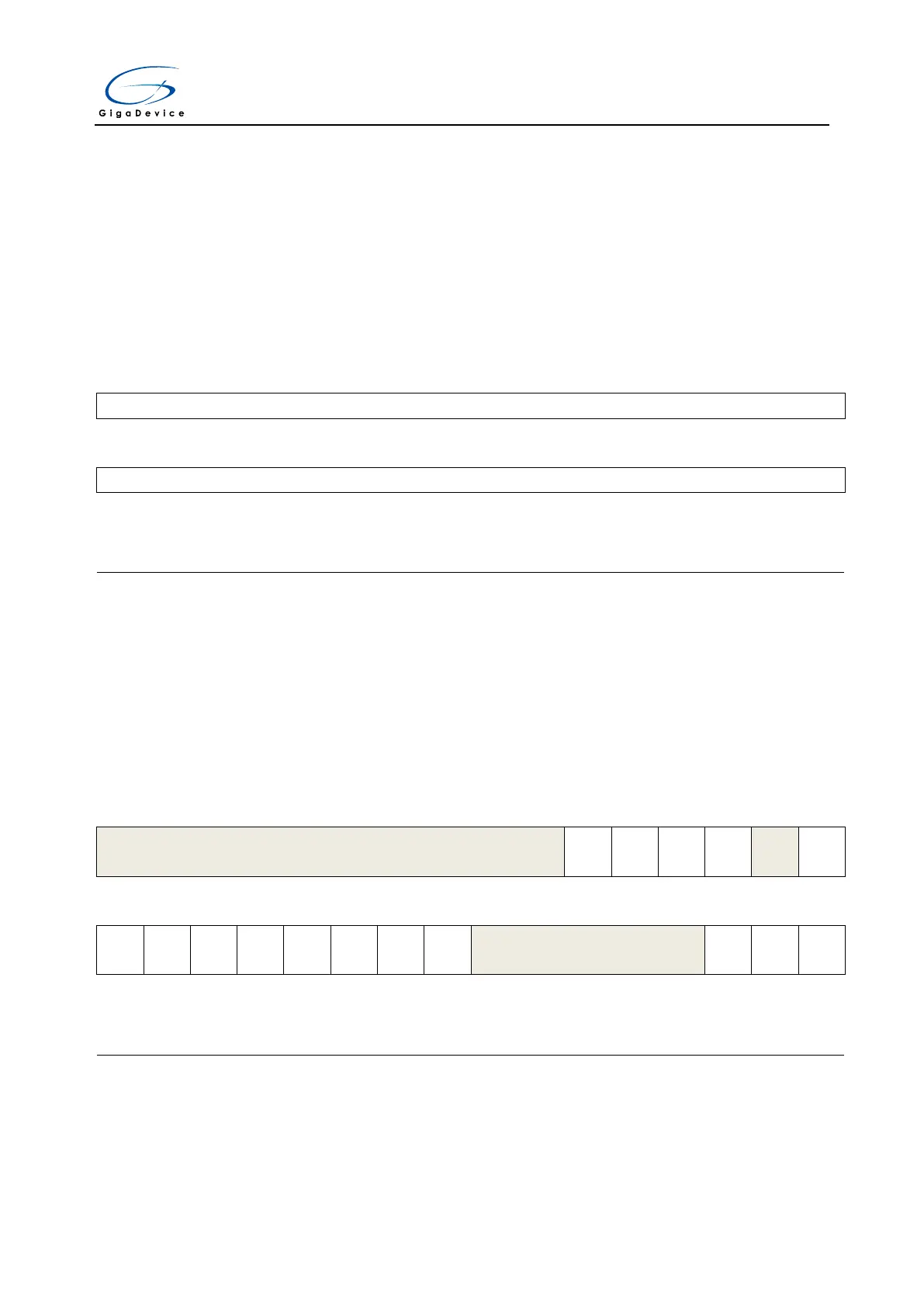

10.4.2. Control register (DBG_CTL)

Address offset: 0x04

Reset value: 0x0000 0000; power reset only

This register has to be accessed by word(32-bit)

Must be kept at reset value

This bit is set and reset by software

0: no effect

Loading...

Loading...