GD32VF103 User Manual

448

This register has to be accessed by word(32-bit)

Must be kept at reset value

This bit is set by the software to start dequeuing a frame from receive FIFO1.

This bit is reset by the hardware while the dequeuing is done.

This bit is set by hardware when receive FIFO1 is overfull and reset by software

when write 1 to this bit.

0: The receive FIFO1 is not overfull

1: The receive FIFO1 is overfull

This bit is set by hardware when receive FIFO1 is full and reset by software when

write 1 to this bit.

0: The receive FIFO1 is not full

1: The receive FIFO1 is full

Must be kept at reset value

These bits are the length of the receive FIFO1.

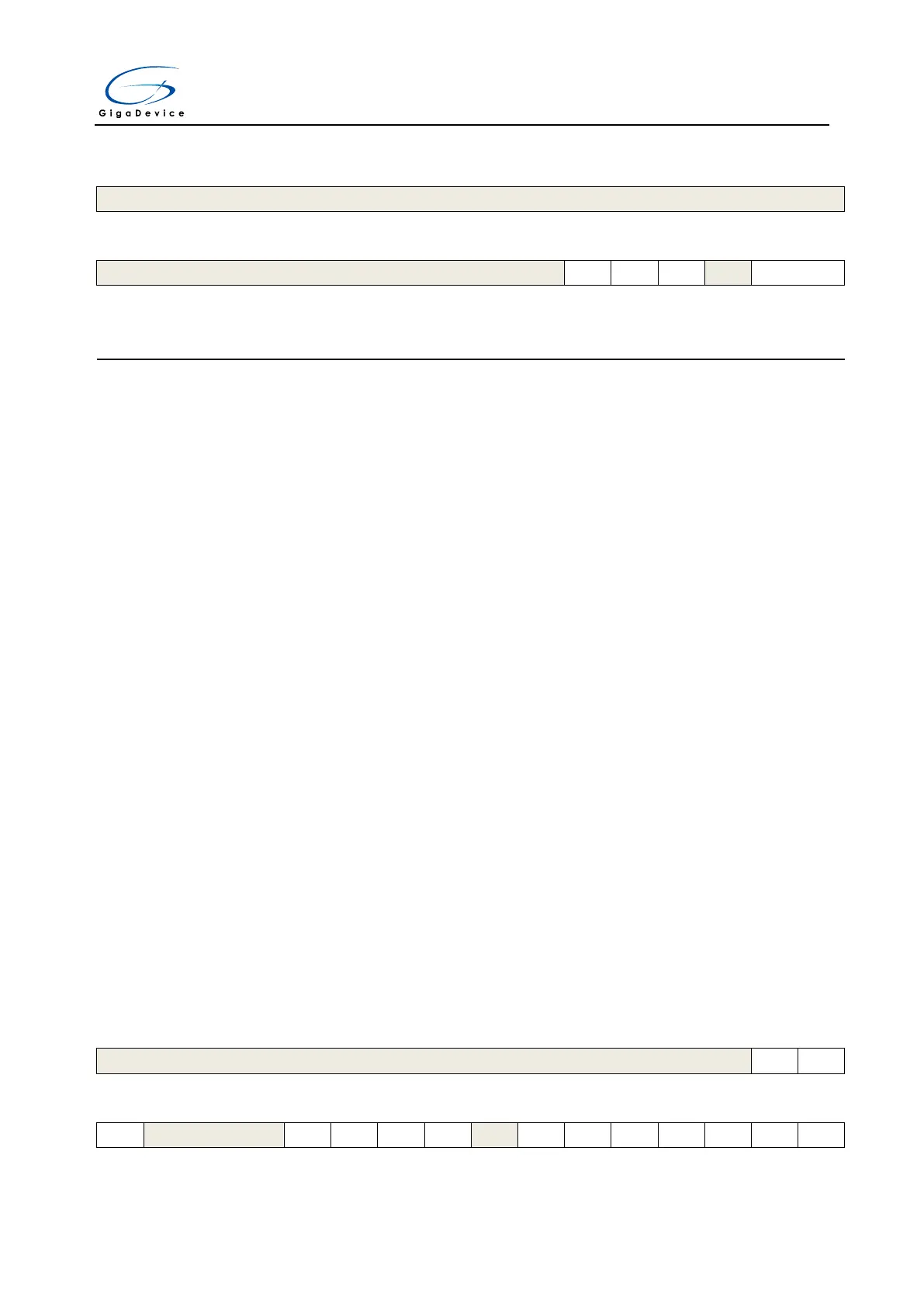

20.4.6. Interrupt enable register (CAN_INTEN)

Address offset: 0x14

Reset value: 0x0000 0000

This register has to be accessed by word(32-bit)

Loading...

Loading...