GD32VF103 User Manual

232

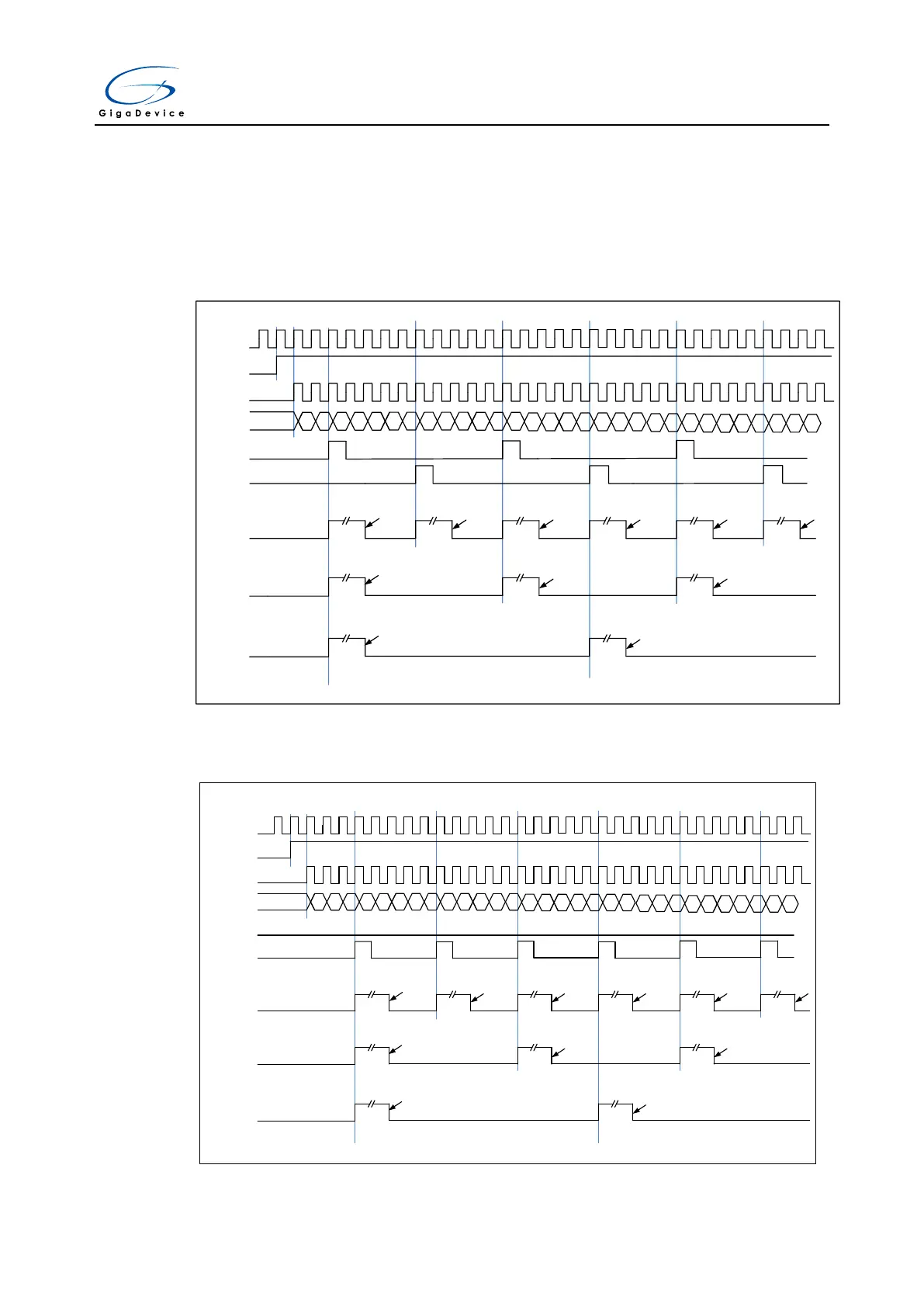

For odd values of CREP in center-aligned mode, the update event occurs either on the

overflow or on the underflow depending on when the CREP register was written and when

the counter was started. The update event is generated at overflow when the CREP was

written before starting the counter and generated at underflow when the CREP was written

after starting the counter.

Figure 15-9. Repetition counter timing chart of center-aligned counting mode

CEN

03 02 01 00 01 02

….

62 63 62 61

….

01 00

Underflow

Overflow

TIMERx_CREP = 0x0

TIMER_CK

01

02

….

62 63 62

61

UPIF

TIMERx_CREP = 0x1

….

01 00

01

02

….

62 63 62

61

UPIF

UPIF

TIMERx_CREP = 0x2

CNT_CLK

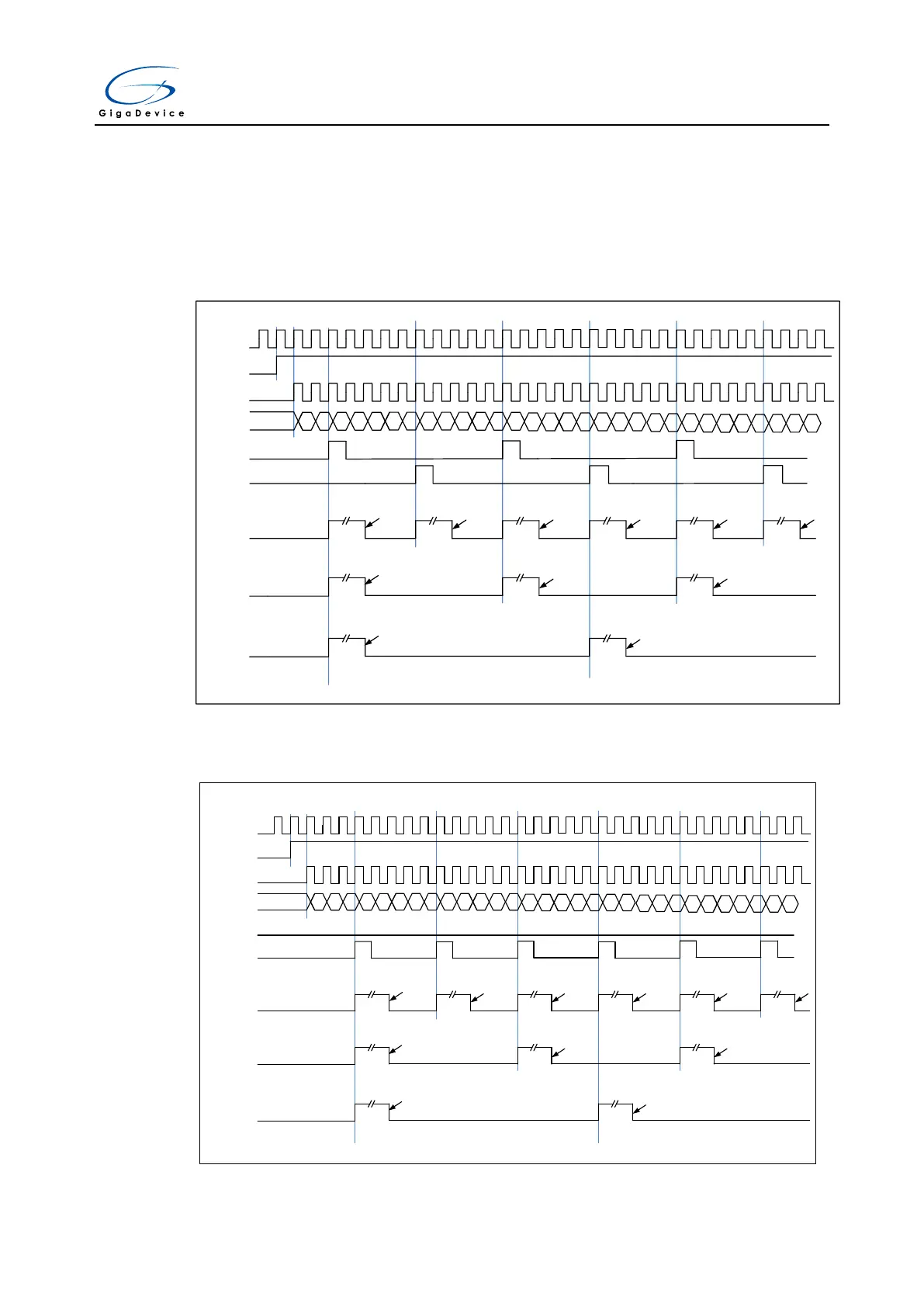

Figure 15-10. Repetition counter timing chart of up counting mode

CEN

CNT_REG

60 61 62 63 00 01

…

62 63 00 01

…

62 63

Underflow

Overflow

TIMERx_CREP = 0x0

TIMER_CK

00

01

…

62 63 00

01

UPIF

TIMERx_CREP = 0x1

…

62 63

00

01

…

62 63 00

01

UPIF

UPIF

TIMERx_CREP = 0x2

CNT_CLK

Loading...

Loading...