GD32VF103 User Manual

25

the same memory address space but in different address ranges. Program memory, data

memory, registers and I/O ports are organized within the same linear 4-Gbyte address

space .The maximum address range of the RISC-V is 4-Gbyte due to its 32-bit bus address

width. Additionally, a pre-defined memory map is provided by the RISC-V processor to reduce

the software complexity of repeated implementation for different device vendors. In the map,

some regions are used by the RISC-V system peripherals which can not be modified.

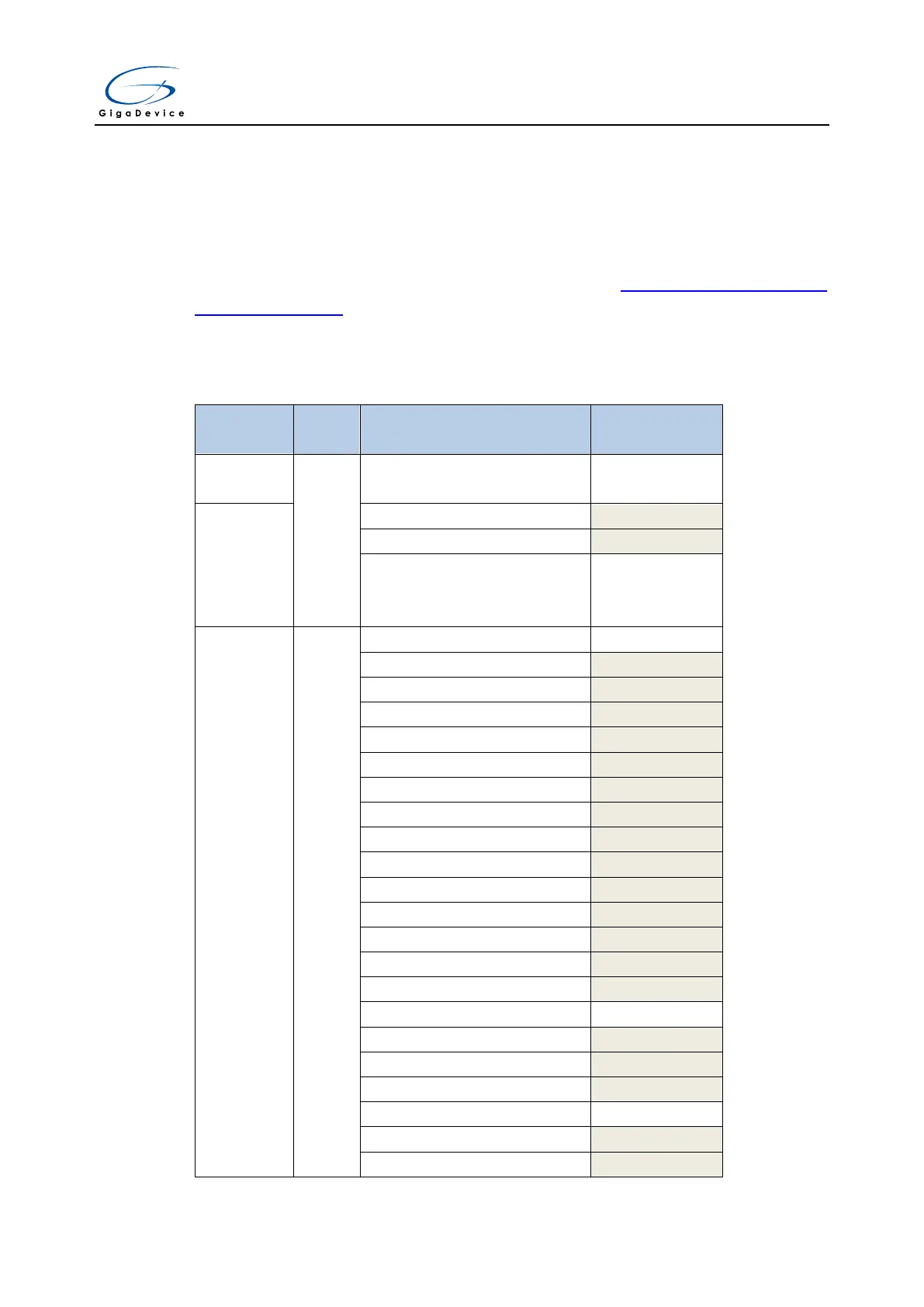

However, the other regions are available to the vendors. Table 1-2. Memory map of

GD32VF103 devices shows the memory map of the GD32VF103 series devices, including

Code, SRAM, peripheral, and other pre-defined regions. Almost each peripheral is allocated

1KB of space. This allows simplifying the address decoding for each peripheral.

Table 1-2. Memory map of GD32VF103 devices

0xA000 0000 - 0xA000 0FFF

0x9000 0000 - 0x9FFF FFFF

0x7000 0000 - 0x8FFF FFFF

0x6000 0000 - 0x6FFF FFFF

0x5000 0000 - 0x5003 FFFF

0x4008 0000 - 0x4FFF FFFF

0x4004 0000 - 0x4007 FFFF

0x4002 BC00 - 0x4003 FFFF

0x4002 B000 - 0x4002 BBFF

0x4002 A000 - 0x4002 AFFF

0x4002 8000 - 0x4002 9FFF

0x4002 6800 - 0x4002 7FFF

0x4002 6400 - 0x4002 67FF

0x4002 6000 - 0x4002 63FF

0x4002 5000 - 0x4002 5FFF

0x4002 4000 - 0x4002 4FFF

0x4002 3C00 - 0x4002 3FFF

0x4002 3800 - 0x4002 3BFF

0x4002 3400 - 0x4002 37FF

0x4002 3000 - 0x4002 33FF

0x4002 2C00 - 0x4002 2FFF

0x4002 2800 - 0x4002 2BFF

0x4002 2400 - 0x4002 27FF

0x4002 2000 - 0x4002 23FF

0x4002 1C00 - 0x4002 1FFF

0x4002 1800 - 0x4002 1BFF

Loading...

Loading...