PCH Pin States

112 Datasheet

NOTES:

1. These signals can be configured as outputs in GPIO mode.

2. This signal is sampled as a functional strap during Reset. Refer to Functional straps

definition table for usage.

3. External Termination is required for JTAG enabling.

4. Not all signals or pin functionalities may be available on a given SKU. See Section 1.3 and

Chapter 2 for details.

§ §

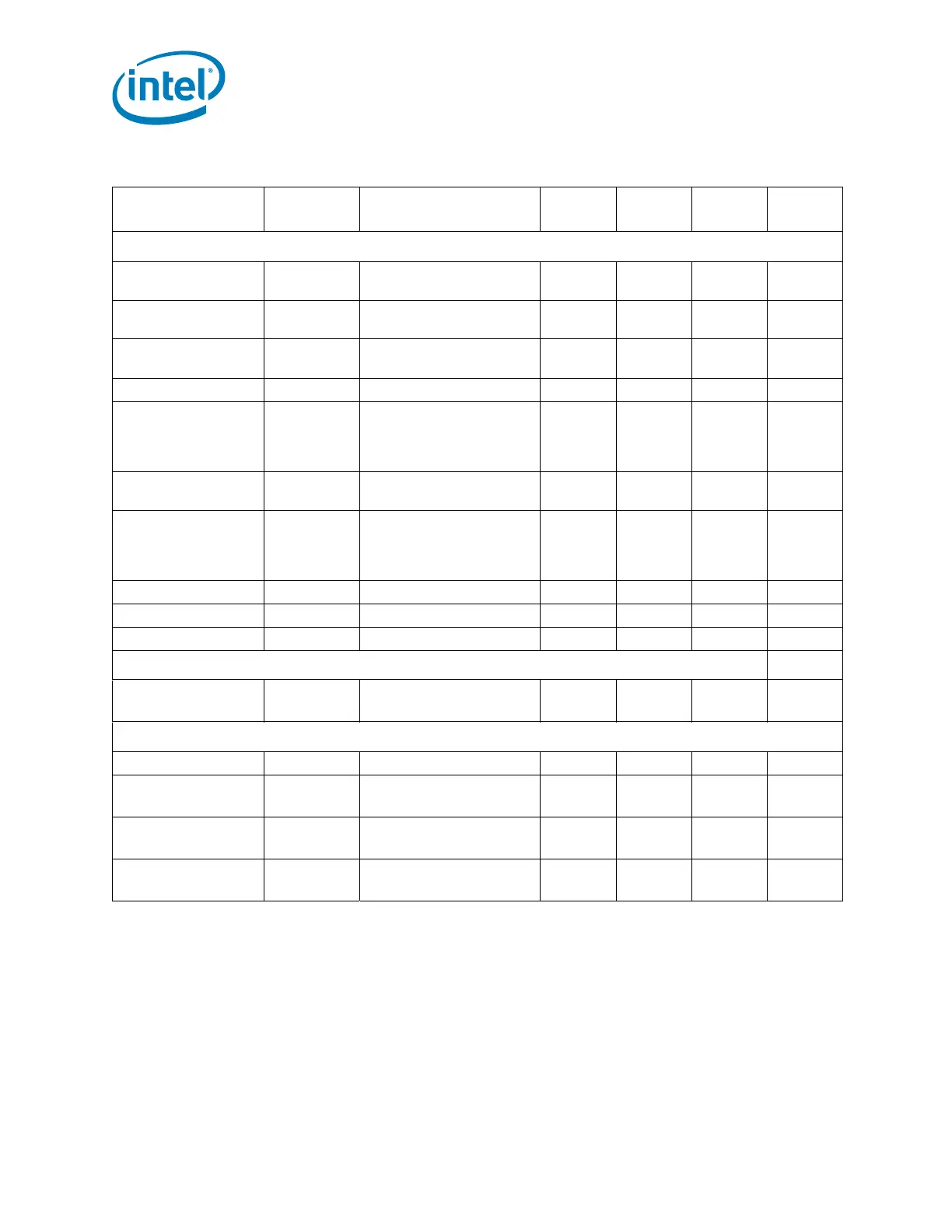

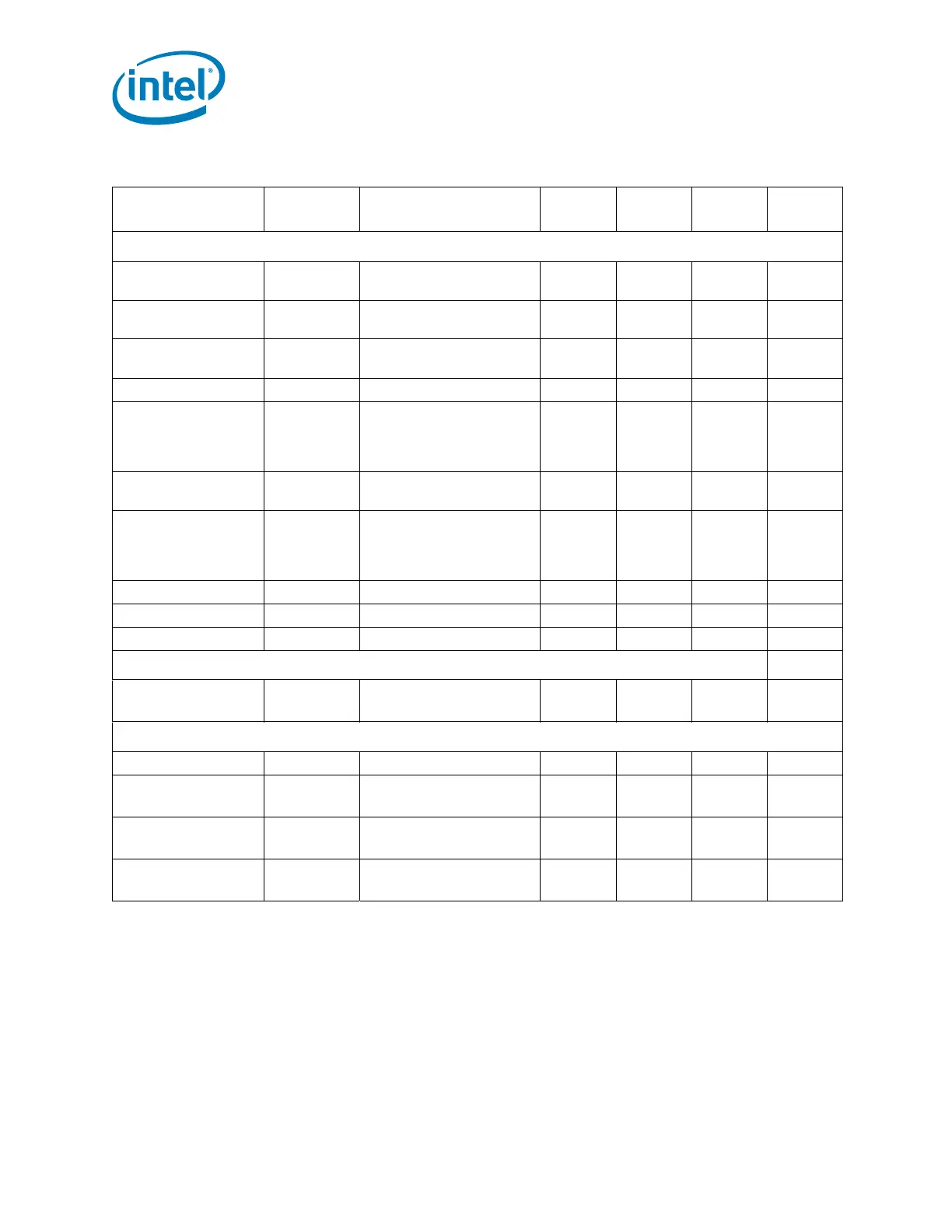

Clock Interface

CLKIN_DMI_P,

CLKIN_DMI_N

Core External pull-down Low Low Off Off

CLKIN_SATA_N/

CLKIN_SATA_P/

Core External pull-down Low Low Off Off

CLKIN_DOT_96P,

CLKIN_DOT_96N

Core External pull-down Low Low Off Off

CLKIN_PCILOOPBACK Core Clock Generator Running Running Off Off

PCIECLKRQ[7:3]#/

GPIO[46:44,26:25]

1

,

PCIECLKRQ0#/

GPIO73

1

Suspend External Pull-up Driven Driven Driven Driven

PCIECLKRQ[2:1]#/

GPIO[20:18]

1

Core External Pull-up Driven Driven Off Off

PEG_A_CLKRQ#/

GPIO47

1

,

PEG_B_CLKRQ#/

GPIO56

1

Suspend External Pull-up Driven Driven Driven Driven

XTAL25_IN Core Clock Generator High-Z High-Z Off Off

REFCLK14IN Core External pull-down Low Low Off Off

CLKIN_PCILOOPBACK Core Clock Generator High-Z High-Z Off Off

Intel

®

Flexible Display Interface

FDI_RXP[7:0],

FDI_RXN[7:0]

Core Processor Driven Driven Off Off

Digital Display Interface

DDP[B:C:D]_HPD Core External Pull-down Driven Driven Off Off

SDVO_INTP,

SDVO_INTN

Core SDVO controller device Driven Driven Off Off

SDVO_TVCLKINP,

SDVO_TVCLKINN

Core SDVO controller device Driven Driven Off Off

SDVO_STALLP,

SDVO_STALLN

Core SDVO controller device Driven Driven Off Off

Table 3-5. Power Plane for Input Signals for Mobile Configurations (Sheet 3 of 3)

Signal Name Power Well Driver During Reset

C-x

states

S0/S1 S3 S4/S5

Loading...

Loading...