Datasheet 195

Functional Description

5.16.8.2.4 Non-AHCI Mode PME# Generation

When in non-AHCI mode (legacy mode) of operation, the SATA controller does not

generate PME#. This includes attach events (since the port must be disabled), or

interlock switch events (using the SATAGP pins).

5.16.8.3 SMI Trapping (APM)

Device 31:Function2:Offset C0h (see Section 14.1.39) contain control for generating

SMI# on accesses to the IDE I/O spaces. These bits map to the legacy ranges (1F0–

1F7h, 3F6h, 170–177h, and 376h) and native IDE ranges defined by PCMDBA, PCTLBA,

SCMDBA an SCTLBA. If the SATA controller is in legacy mode and is using these

addresses, accesses to one of these ranges with the appropriate bit set causes the

cycle to not be forwarded to the SATA controller, and for an SMI# to be generated. If an

access to the Bus-Master IDE registers occurs while trapping is enabled for the device

being accessed, then the register is updated, an SMI# is generated, and the device

activity status bits (Section 14.1.40) are updated indicating that a trap occurred.

5.16.9 SATA Device Presence

In legacy mode, the SATA controller does not generate interrupts based on hot plug/

unplug events. However, the SATA PHY does know when a device is connected (if not in

a partial or slumber state), and it s beneficial to communicate this information to host

software as this will greatly reduce boot times and resume times.

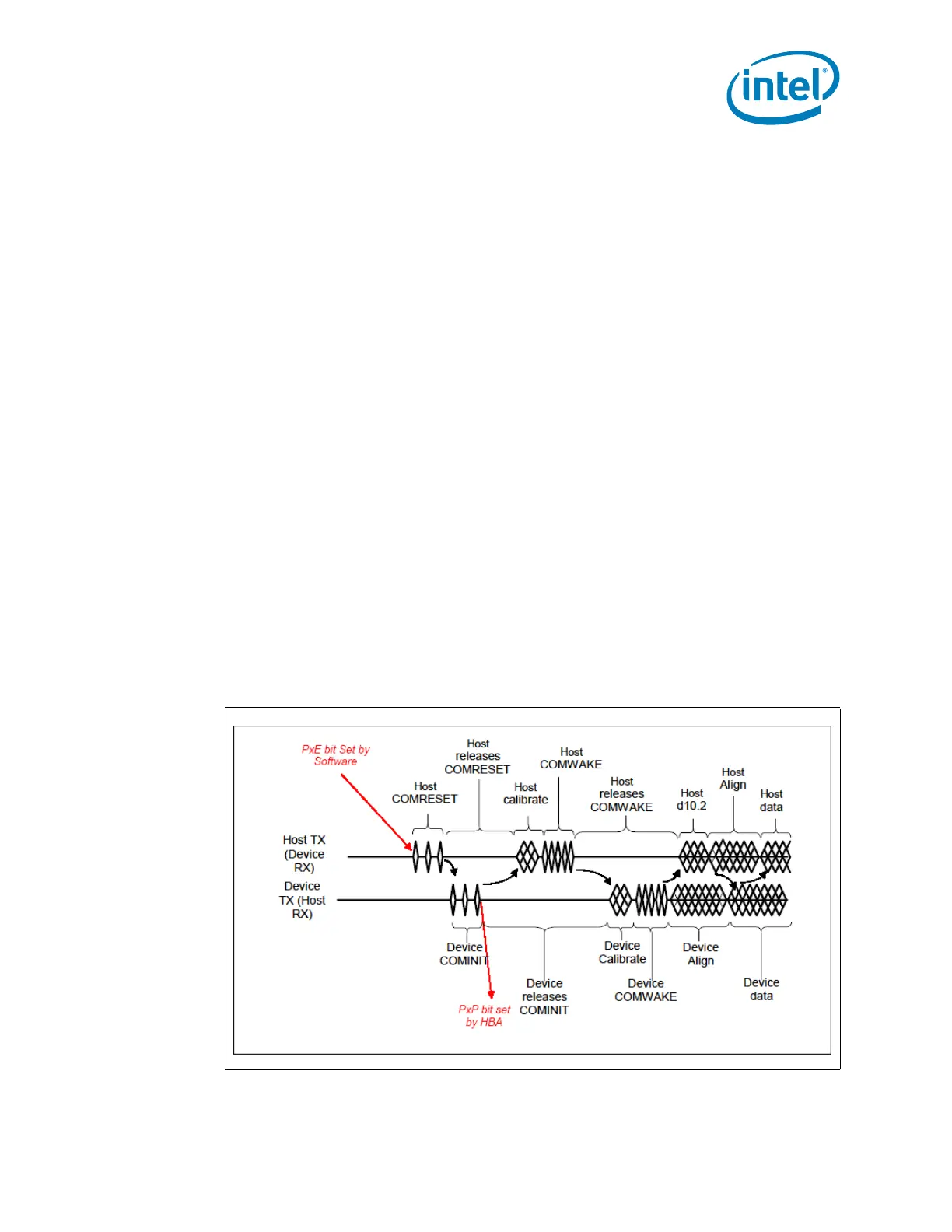

The flow used to indicate SATA device presence is shown in Figure 5-8. The ‘PxE’ bit

refers to PCS.P[3:0]E bits, depending on the port being checked and the ‘PxP’ bits refer

to the PCS.P[3:0]P bits, depending on the port being checked. If the PCS/PxP bit is set

a device is present, if the bit is cleared a device is not present. If a port is disabled,

software can check to see if a new device is connected by periodically re-enabling the

port and observing if a device is present, if a device is not present it can disable the

port and check again later. If a port remains enabled, software can periodically poll

PCS.PxP to see if a new device is connected.

Figure 5-8. Flow for Port Enable / Device Present Bits

Loading...

Loading...