Functional Description

218 Datasheet

I

2

C Read

This command allows the PCH to perform block reads to certain I

2

C devices, such as

serial E

2

PROMs. The SMBus Block Read supports the 7-bit addressing mode only.

However, this does not allow access to devices using the I

2

C “Combined Format” that

has data bytes after the address. Typically these data bytes correspond to an offset

(address) within the serial memory chips.

Note: This command is supported independent of the setting of the I2C_EN bit. The I

2

C Read

command with the PEC_EN bit set produces undefined results. Software must force

both the PEC_EN and AAC bit to 0 when running this command.

For I

2

C Read command, the value written into bit 0 of the Transmit Slave Address

Register (SMB I/O register, offset 04h) needs to be 0.

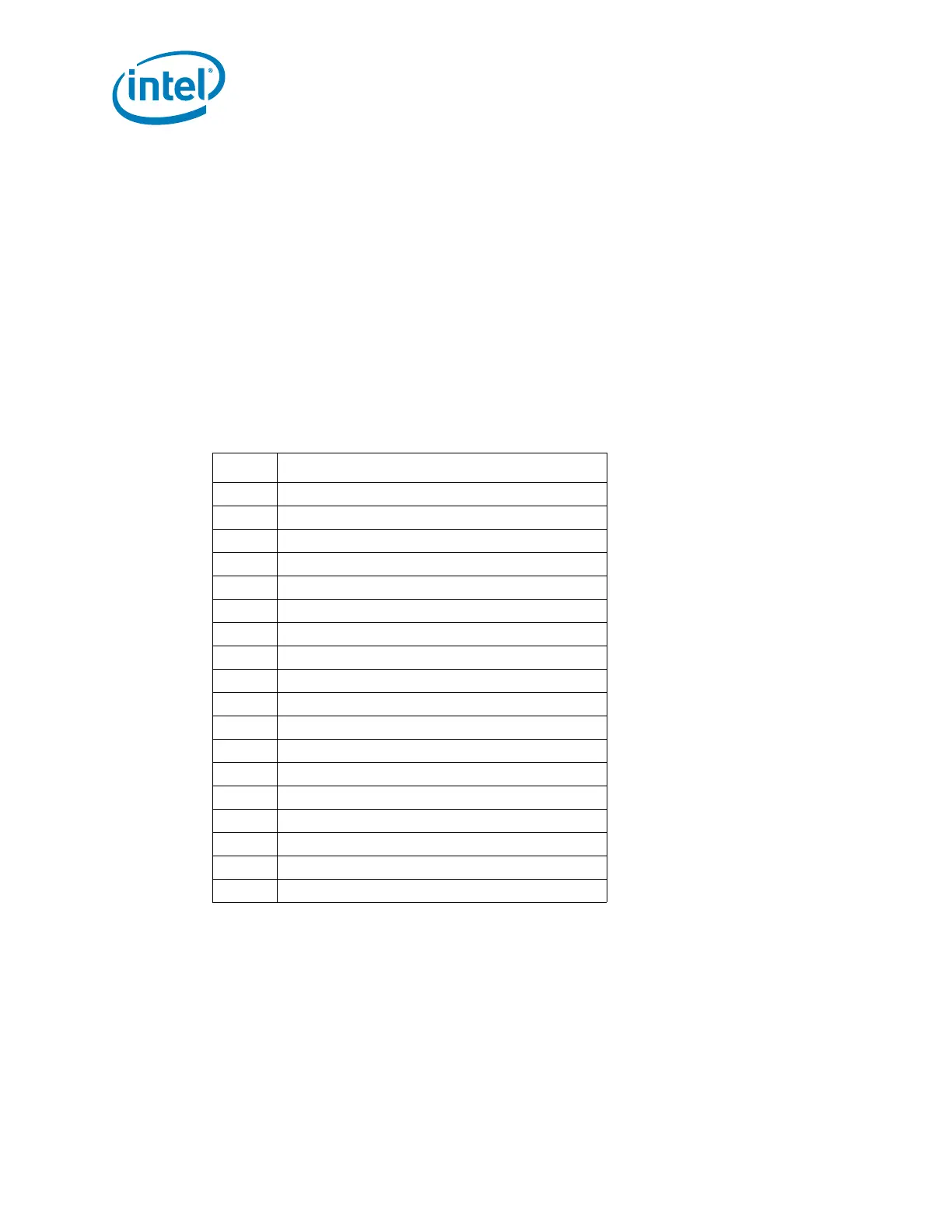

The format that is used for the command is shown in Table 5-44.

The PCH will continue reading data from the peripheral until the NAK is received.

Table 5-44. I

2

C Block Read

Bit Description

1Start

8:2 Slave Address – 7 bits

9Write

10 Acknowledge from slave

18:11 Send DATA1 register

19 Acknowledge from slave

20 Repeated Start

27:21 Slave Address – 7 bits

28 Read

29 Acknowledge from slave

37:30 Data byte 1 from slave – 8 bits

38 Acknowledge

46:39 Data byte 2 from slave – 8 bits

47 Acknowledge

– Data bytes from slave / Acknowledge

– Data byte N from slave – 8 bits

– NOT Acknowledge

–Stop

Loading...

Loading...