Datasheet 131

Functional Description

5.4.1.3 Cycle Type / Direction (CYCTYPE + DIR)

The PCH always drives Bit 0 of this field to 0. Peripherals running bus master cycles

must also drive Bit 0 to 0. Table 5-9 shows the valid bit encodings.

5.4.1.4 Size

Bits[3:2] are reserved. The PCH always drives them to 00. Peripherals running bus

master cycles are also supposed to drive 00 for Bits 3:2; however, the PCH ignores

those bits. Bits[1:0] are encoded as listed in Table 5-10.

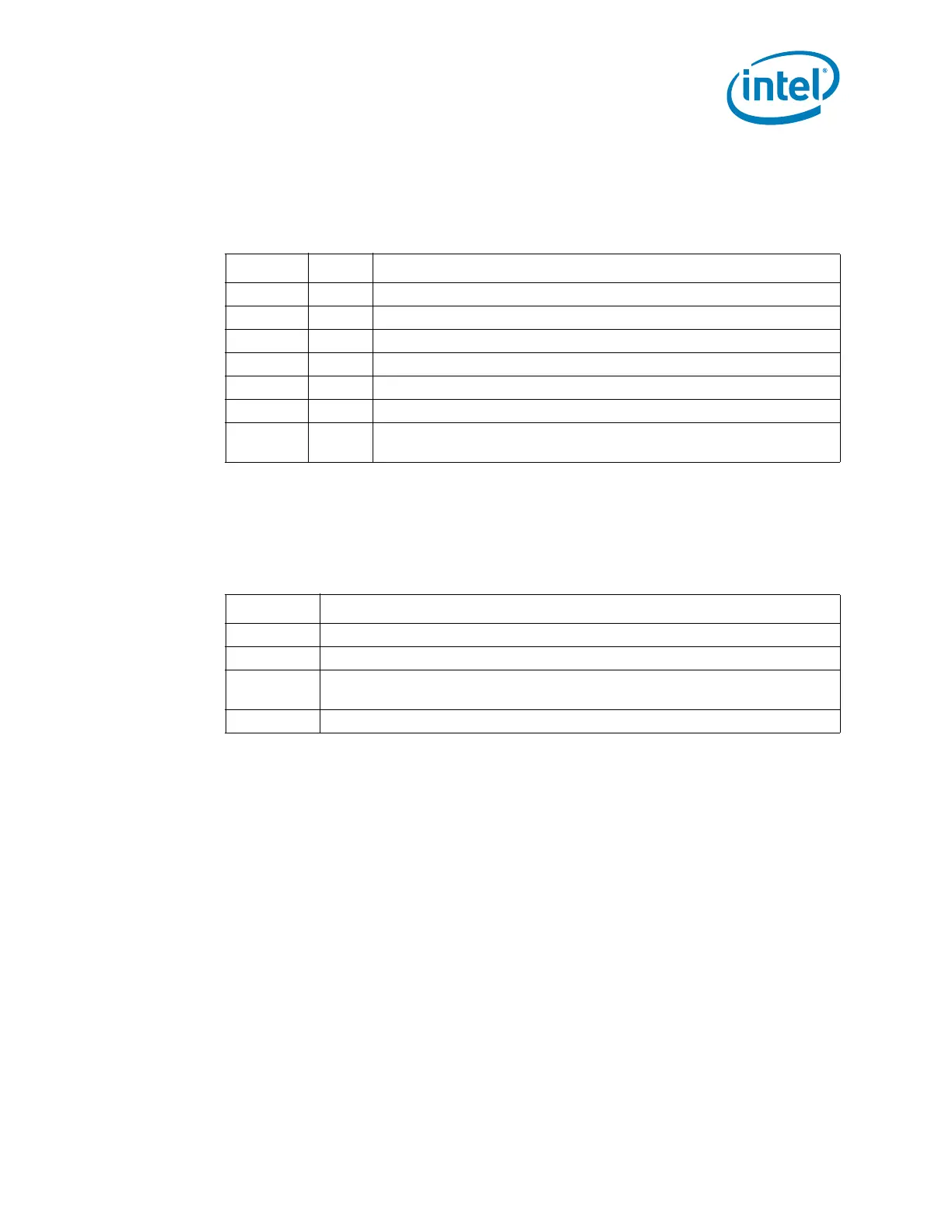

Table 5-9. Cycle Type Bit Definitions

Bits[3:2] Bit1 Definition

00 0 I/O Read

00 1 I/O Write

01 0 Memory Read

01 1 Memory Read

10 0 DMA Read

10 1 DMA Write

11 x

Reserved. If a peripheral performing a bus master cycle generates this

value, the PCH aborts the cycle.

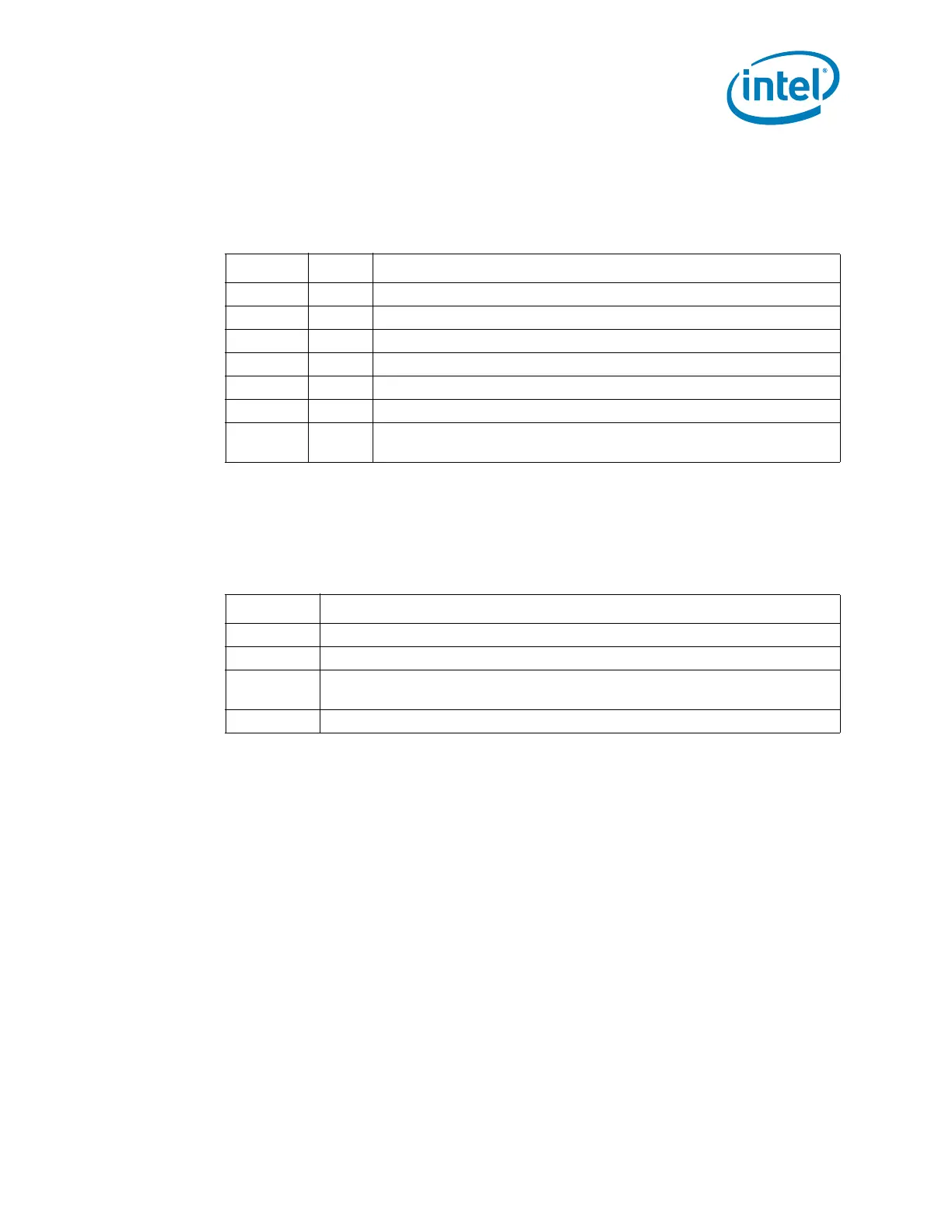

Table 5-10. Transfer Size Bit Definition

Bits[1:0] Size

00 8-bit transfer (1 byte)

01 16-bit transfer (2 bytes)

10

Reserved. The PCH never drives this combination. If a peripheral running a bus

master cycle drives this combination, the PCH may abort the transfer.

11 32-bit transfer (4 bytes)

Loading...

Loading...