Datasheet 493

LPC Interface Bridge Registers (D31:F0)

13.5 Advanced Programmable Interrupt Controller

(APIC)

13.5.1 APIC Register Map

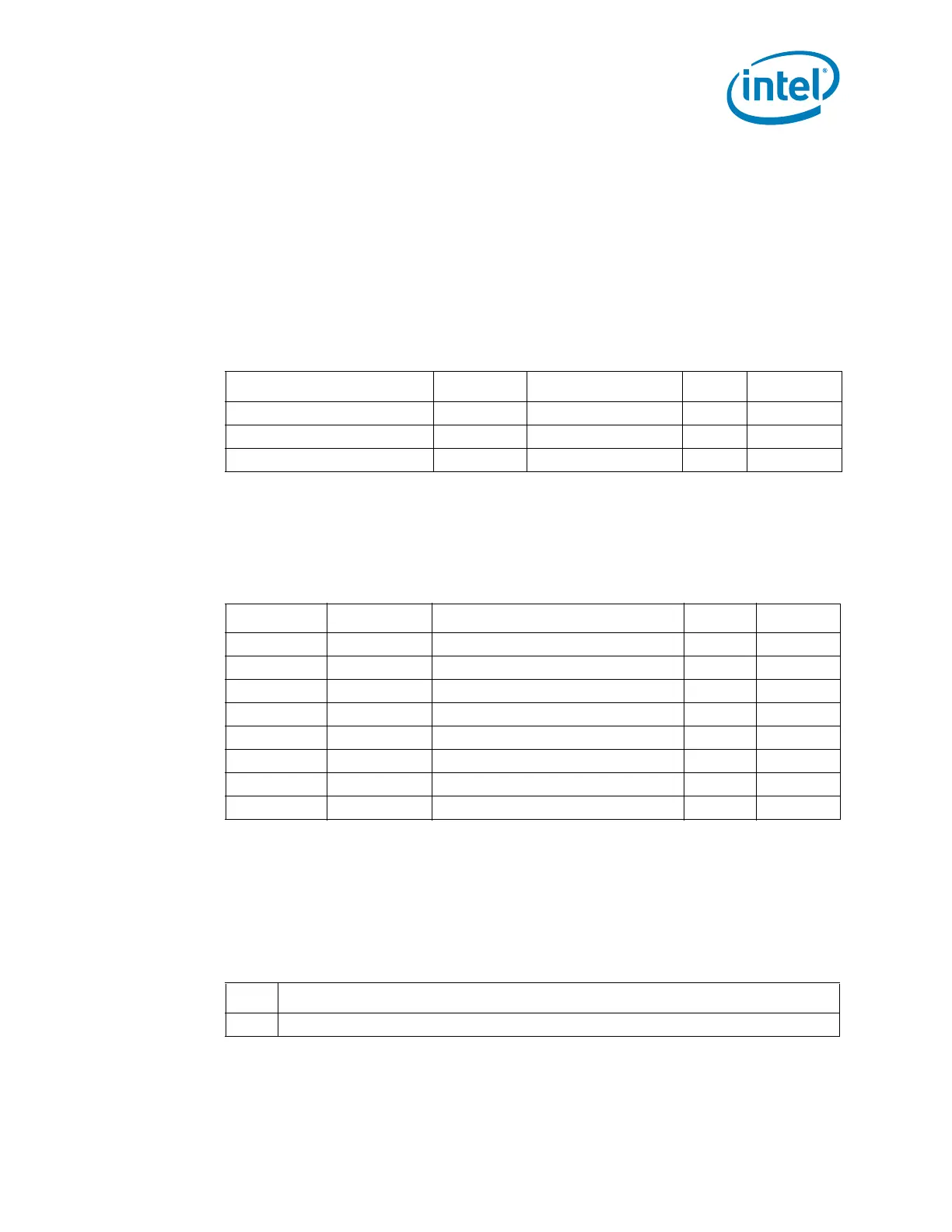

The APIC is accessed using an indirect addressing scheme. Two registers are visible by

software for manipulation of most of the APIC registers. These registers are mapped

into memory space. The address bits 19:12 of the address range are programmable

through bits 7:0 of OIC register (Chipset Config Registers:Offset 31FEh) The registers

are shown in Table 13-4.

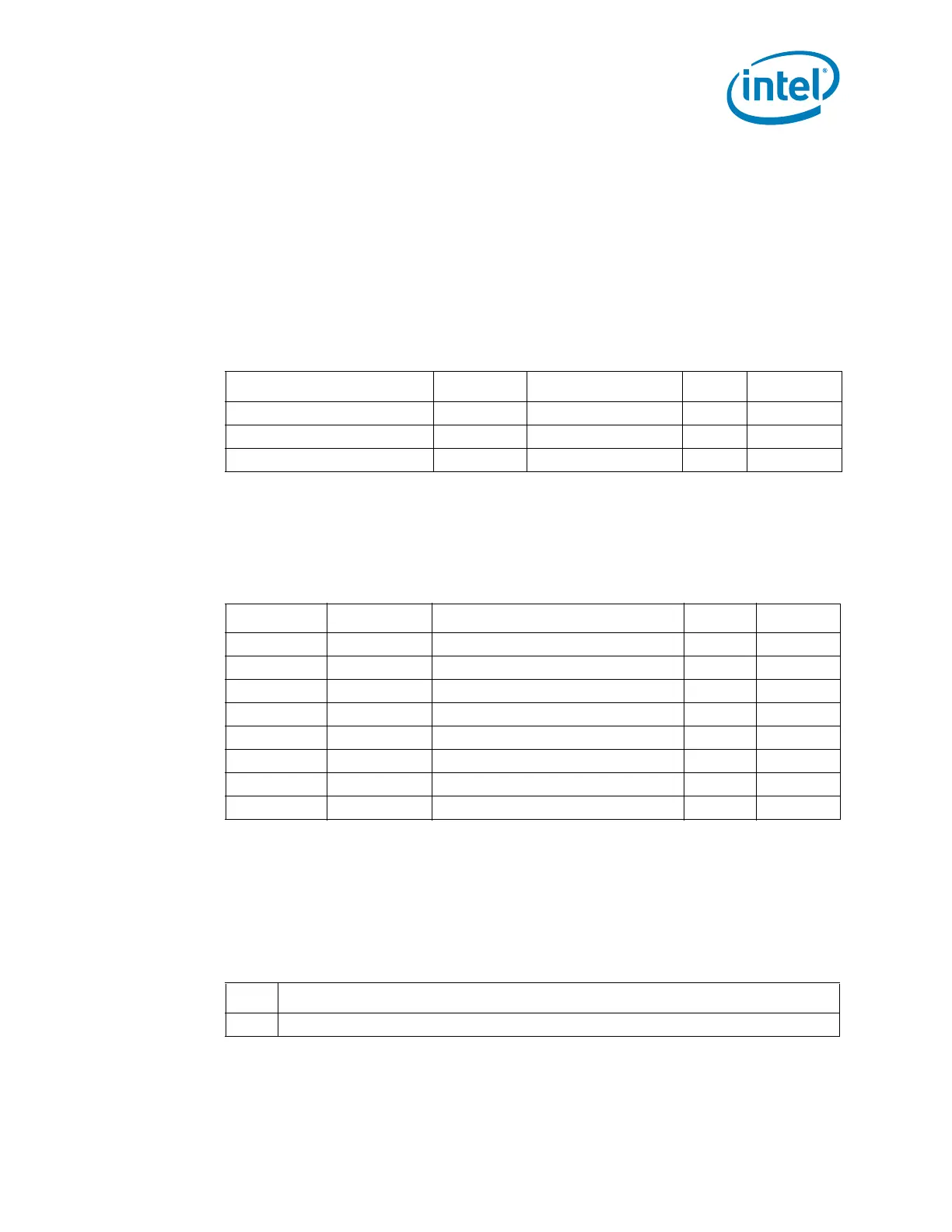

Table 13-5 lists the registers which can be accessed within the APIC using the Index

Register. When accessing these registers, accesses must be done one DWord at a time.

For example, software should never access byte 2 from the Data register before

accessing bytes 0 and 1. The hardware will not attempt to recover from a bad

programming model in this case.

13.5.2 IND—Index Register

Memory Address FEC_ _0000h Attribute: R/W

Default Value: 00hSize: 8 bits

The Index Register will select which APIC indirect register to be manipulated by

software. The selector values for the indirect registers are listed in Table 13-5. Software

will program this register to select the desired APIC internal register

.

Table 13-4. APIC Direct Registers

Address Mnemonic Register Name Size Type

FEC_ _0000h IND Index 8 bits R/W

FEC_ _0010h DAT Data 32 bits R/W

FEC_ _0040h EOIR EOI 32 bits WO

Table 13-5. APIC Indirect Registers

Index Mnemonic Register Name Size Type

00 ID Identification 32 bits R/W

01 VER Version 32 bits RO

02–0F — Reserved — RO

10–11 REDIR_TBL0 Redirection Table 0 64 bits R/W, RO

12–13 REDIR_TBL1 Redirection Table 1 64 bits R/W, RO

... ... ... ... ...

3E–3F REDIR_TBL23 Redirection Table 23 64 bits R/W, RO

40–FF — Reserved — RO

Bit Description

7:0 APIC Index — R/W. This is an 8-bit pointer into the I/O APIC register table.

Loading...

Loading...