Functional Description

160 Datasheet

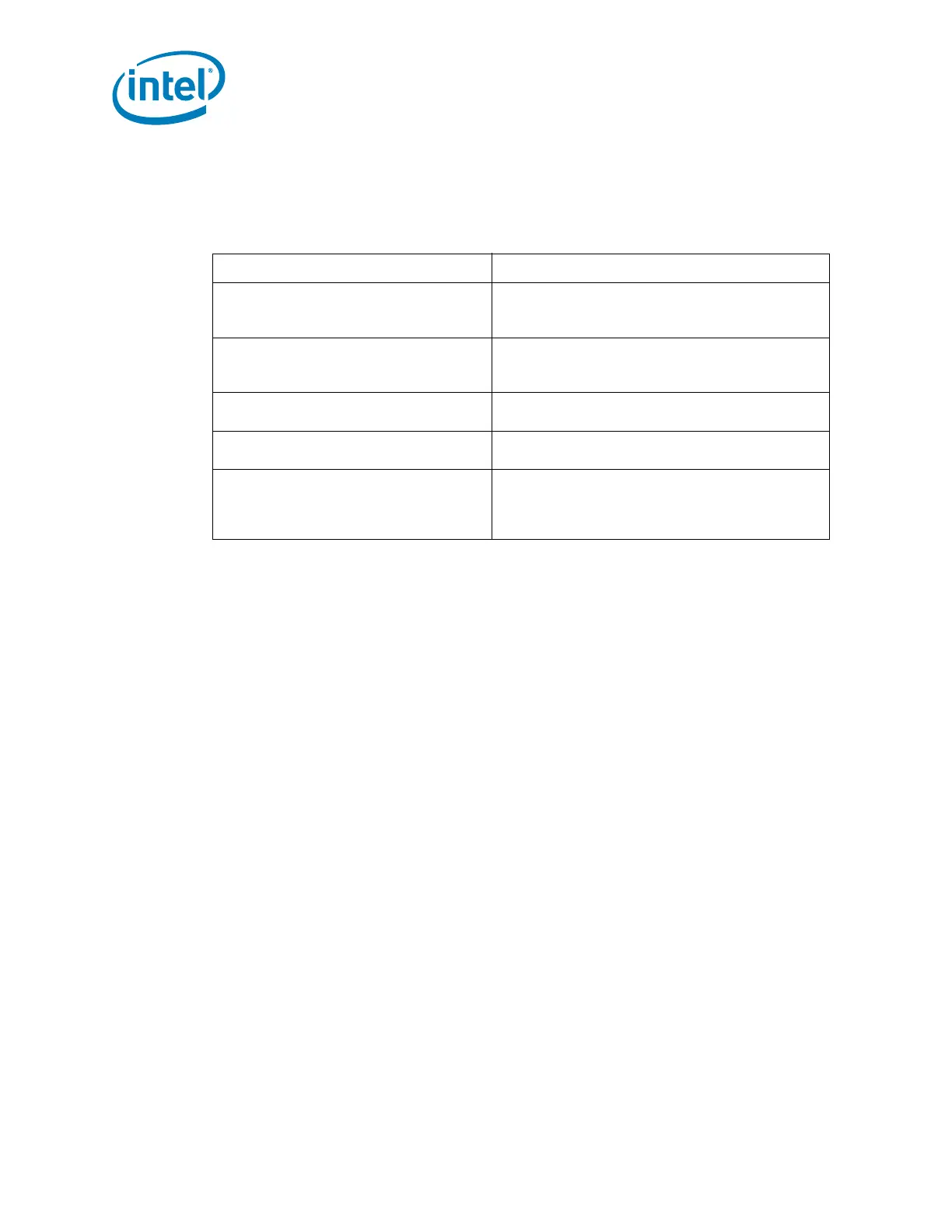

5.12.1.4 NMI (Non-Maskable Interrupt)

Non-Maskable Interrupts (NMIs) can be generated by several sources, as described in

Table 5-23.

5.12.1.5 Processor Power Good (PROCPWRGD)

This signal is connected to the processor’s UNCOREPWRGOOD input to indicate when

the processor power is valid.

5.12.2 Dual-Processor Issues

5.12.2.1 Usage Differences

In dual-processor designs, some of the processor signals are unused or used differently

than for uniprocessor designs.

• A20M#/A20GATE and FERR# are generally not used, but still supported.

• I/O APIC and SMI# are assumed to be used.

5.12.3 Virtual Legacy Wire (VLW) Messages

The PCH supports VLW messages as alternative method of conveying the status of the

following legacy sideband interface signals to the processor:

• A20M#, INTR, SMI#, INIT#, NMI

Note: IGNNE# VLW message is not required to be generated by the PCH as it is internally

emulated by the processor.

VLW are inbound messages to the processor. They are communicated using Vendor

Defined Message over the DMI link.

Legacy processor signals can only be delivered using VLW in the PCH. Delivery of

legacy processor signals (A20M#, INTR, SMI#, INIT# or NMI) using I/O APIC controller

is not supported.

Table 5-23. NMI Sources

Cause of NMI Comment

SERR# goes active (either internally,

externally using SERR# signal, or using

message from processor)

Can instead be routed to generate an SCI, through

the NMI2SCI_EN bit (Device 31:Function 0, TCO

Base + 08h, Bit 11).

IOCHK# goes active using SERIRQ#

stream (ISA system Error)

Can instead be routed to generate an SCI, through

the NMI2SCI_EN bit (Device 31:Function 0, TCO

Base + 08h, Bit 11).

SECSTS Register Device 31: Function F0

Offset 1Eh, bit 8.

This is enabled by the Parity Error Response Bit

(PER) at Device 30: Function 0 Offset 04, bit 6.

DEV_STS Register Device 31:Function F0

Offset 06h, bit 8

This is enabled by the Parity Error Response Bit

(PER) at Device 30: Function 0 Offset 04, bit 6.

GPIO[15:0] when configured as a General

Purpose input and routed as NMI (by

GPIO_ROUT at Device 31: Function 0

Offset B8)

This is enabled by GPI NMI Enable (GPI_NMI_EN)

bits at Device 31: Function 0 Offset: GPIOBASE +

28h bits 15:0

Loading...

Loading...