PCH and System Clocks

116 Datasheet

Table 4-4 provides a basic description of the Spread modulators. The spread

modulators each operate on the XCK PLL’s 2.4 GHz outputs. Spread Spectrum tuning

and adjustment can be made on the fly without a platform reboot using specific

programming sequence to the clock registers.

4.3 Clock Configuration Access Overview

The PCH provides increased flexibility of host equivalent configurability of clocks, using

Intel ME FW.

In the Intel ME FW assisted configuration mode, Control settings for PLLs, Spread

Modulators and other clock configuration registers will be handled by the Intel ME

engine. The parameters to be loaded will reside in the Intel ME data region of the SPI

Flash device. BIOS would only have access to the register set through a set of Intel

MEI

commands to the Intel ME.

4.4 Straps Related to Clock Configuration

The following pin straps apply to clock configuration on PCH. Refer to the Pin-Straps

section of the Signal Description chapter for details.

GPIO8 is no longer needed as a functional strap for Integrated clocking. Integrated

Clock Enable functionality is achieved using soft-strap. The current default is Clock

Enabled.

The following soft-straps are implemented on PCH for Clock Configuration.

Integrated Clocking Profile Select: 3 Profile select bits allow up to 8 different clock

profiles to be specified in the SPI flash device. In addition, 3 RTC well backed host

register bits are also defined for Integrated Clocking Profile Selection through BIOS.

§ §

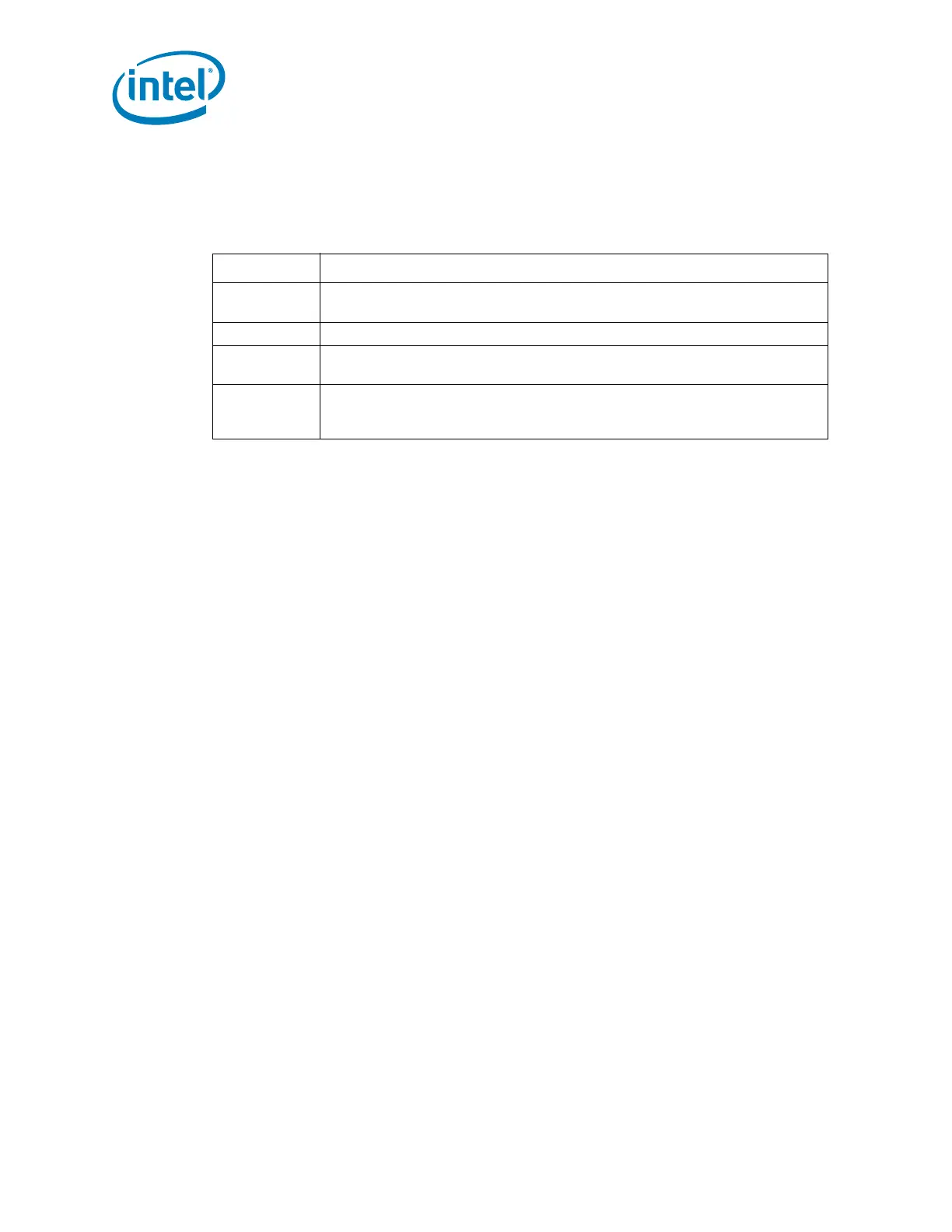

Table 4-4. SSC Blocks

Modulator Description

SSC1

Used for 120 MHz fixed frequency Spread Spectrum Clock. Supports up to

0.5% spread

SSC2 Used for 100 MHz Spread Spectrum Clock. Supports up to 0.5% spread.

SSC3

Used for 133 MHz SSC clock or can be used for 100 MHz fixed frequency SSC

Clock. Supports up to 0.5% spread.

SSC4

Used for 100 MHz fixed frequency SSC clock or can be used for 120 MHz fixed-

frequency super-spread clocks. Supports 0.5% spread for the 100 MHz and up

to 2.5% super-spread for the 120 MHz display clock for Integrated Graphics.

Loading...

Loading...