Datasheet 69

Signal Description

2.13 Miscellaneous Signals

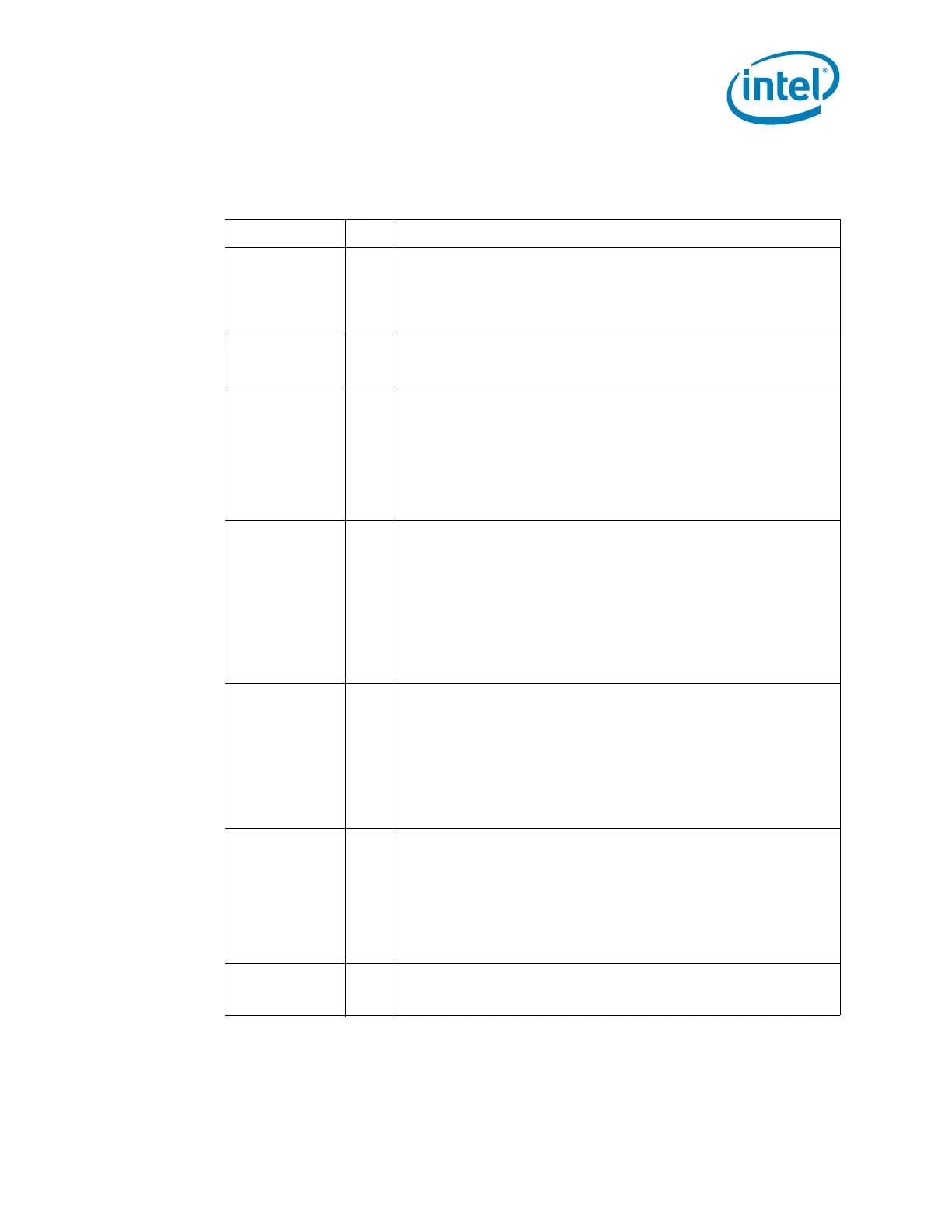

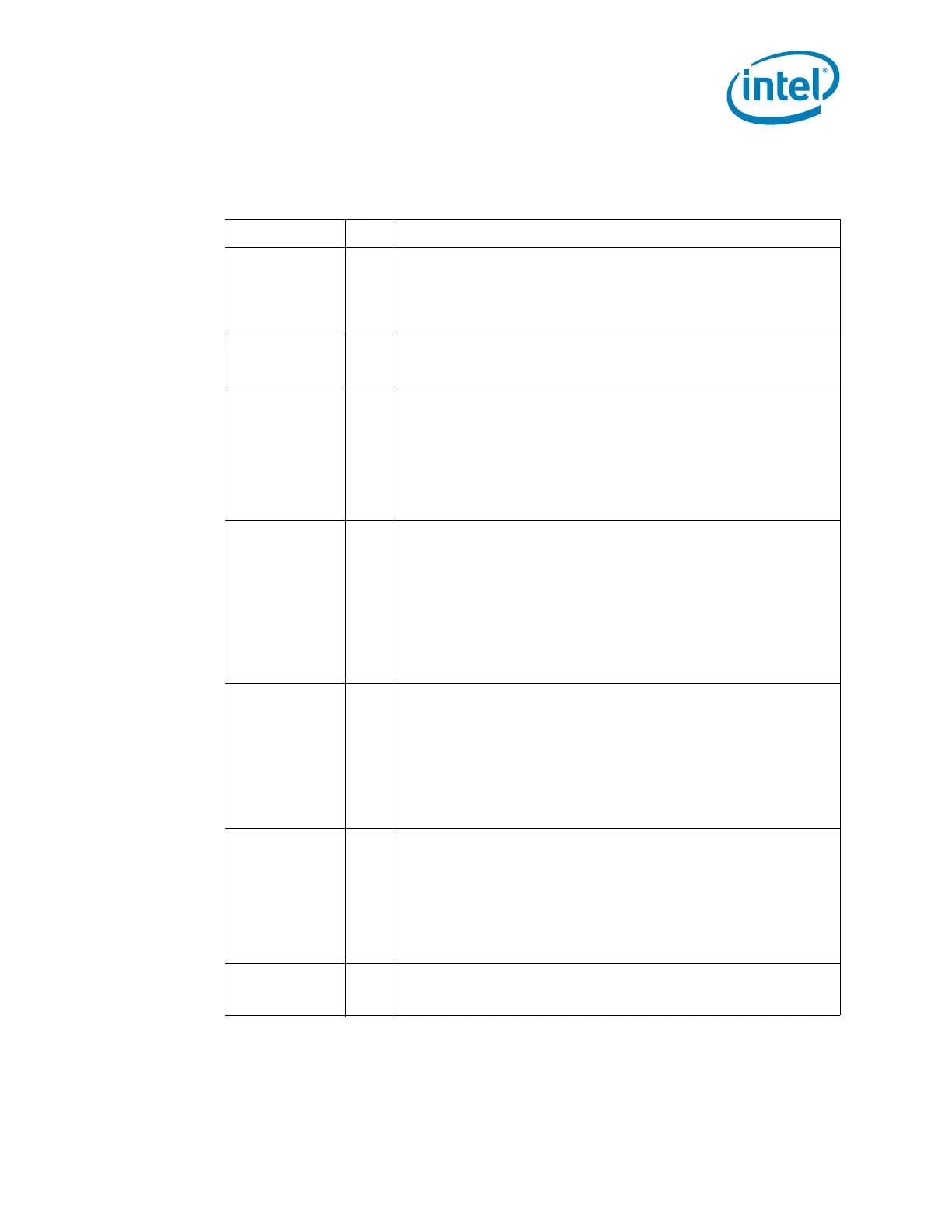

Table 2-13. Miscellaneous Signals

Name Type Description

INTVRMEN I

Internal Voltage Regulator Enable: This signal enables the

internal 1.05 V regulators when pulled high.

This signal must be always pulled-up to VccRTC on desktop platforms

and may optionally be pulled low on mobile platforms if using an

external VR for the DcpSus rail.

DSWVRMEN I

Deep S4/S5 Well Internal Voltage Regulator Enable: This signal

enables the internal DSW 1.05 V regulators.

This signal must be always pulled-up to VccRTC.

SPKR O

Speaker: The SPKR signal is the output of counter 2 and is internally

“ANDed” with Port 61h Bit 1 to provide Speaker Data Enable. This

signal drives an external speaker driver device, which in turn drives

the system speaker. Upon PLTRST#, its output state is 0.

NOTE: SPKR is sampled as a functional strap. See Section 2.27 for

more details. There is a weak integrated pull-down resistor on

SPKR pin.

RTCRST# I

RTC Reset: When asserted, this signal resets register bits in the RTC

well.

NOTES:

1. Unless CMOS is being cleared (only to be done in the G3

power state), the RTCRST# input must always be high when

all other RTC power planes are on.

2. In the case where the RTC battery is dead or missing on the

platform, the RTCRST# pin must rise before the RSMRST#

pin.

SRTCRST# I

Secondary RTC Reset: This signal resets the manageability register

bits in the RTC well when the RTC battery is removed.

NOTES:

1. The SRTCRST# input must always be high when all other RTC

power planes are on.

2. In the case where the RTC battery is dead or missing on the

platform, the SRTCRST# pin must rise before the RSMRST#

pin.

SML1ALERT#/

PCHHOT#/

GPIO74

OD

PCHHOT#: This signal is used to indicate a PCH temperature out of

bounds condition to an external EC, when PCH temperature is greater

than value programmed by BIOS. An external pull-up resistor is

required on this signal.

NOTE: A soft-strap determines the native function SML1ALERT# or

PCHHOT# usage. When soft-strap is 0, function is

SML1ALERT#, when soft-strap is 1, function is PCHHOT#.

INIT3_3V# O

Initialization 3.3 V: INIT3_3V# is asserted by the PCH for 16 PCI

clocks to reset the processor. This signal is intended for Firmware

Hub.

Loading...

Loading...