Datasheet 159

Functional Description

5.12.1.2 INIT (Initialization)

The INIT# VLW Message is asserted based on any one of several events described in

Table 5-22. When any of these events occur, INIT# is asserted for 16 PCI clocks, then

driven high.

Note: INIT3_3V# is functionally identical to INIT# VLW but it is a physical signal at 3.3 V on

desktop SKUs only.

5.12.1.3 FERR# (Numeric Coprocessor Error)

The PCH supports the coprocessor error function with the FERR# message. The

function is enabled using the COPROC_ERR_EN bit. If FERR# is driven active by the

processor, IRQ13 goes active (internally). When it detects a write to the COPROC_ERR

register (I/O Register F0h), the PCH negates the internal IRQ13 and IGNNE# will be

active. IGNNE# remains active until FERR# is driven inactive. IGNNE# is never driven

active unless FERR# is active.

Note: IGNNE# (Ignore Numeric Error is now internally generated by the processor.

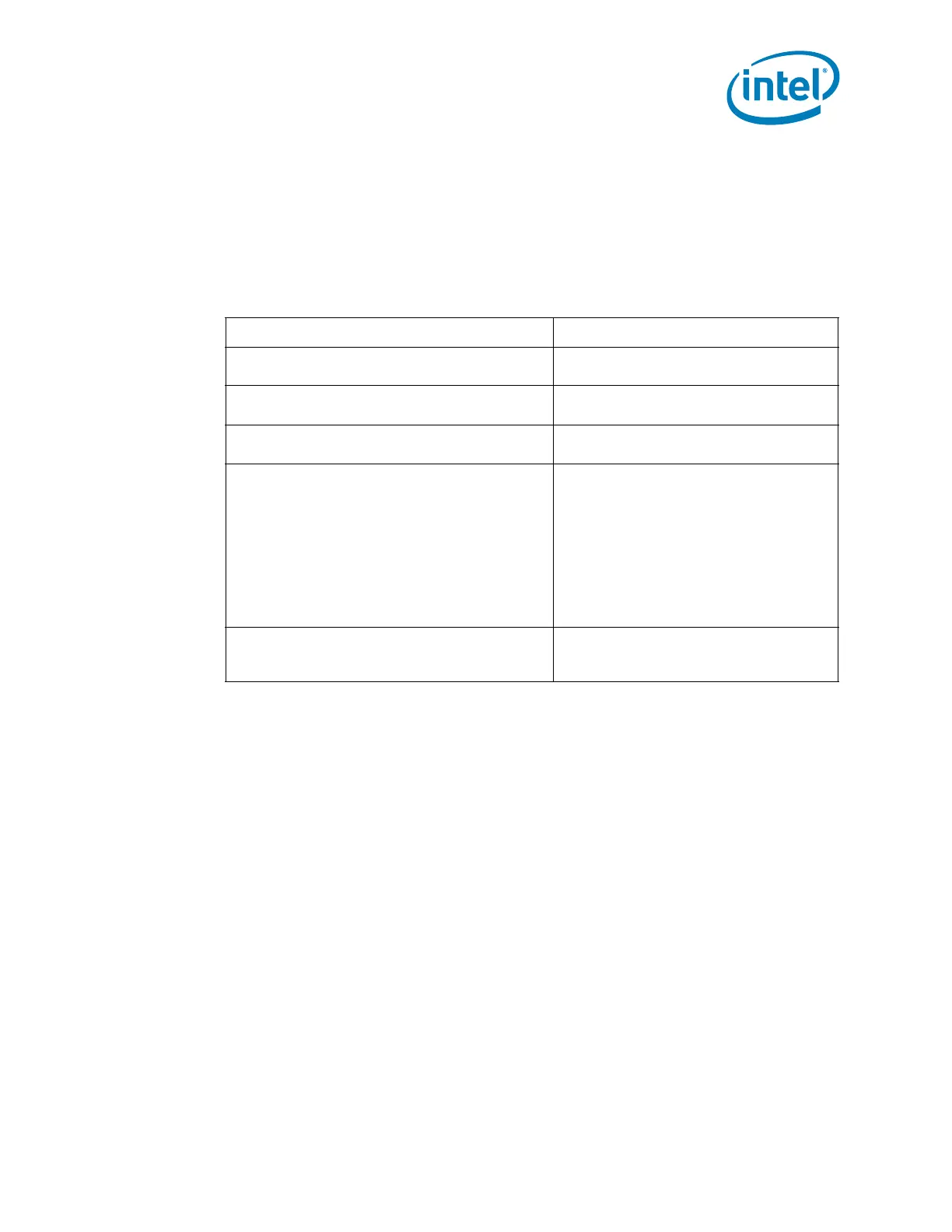

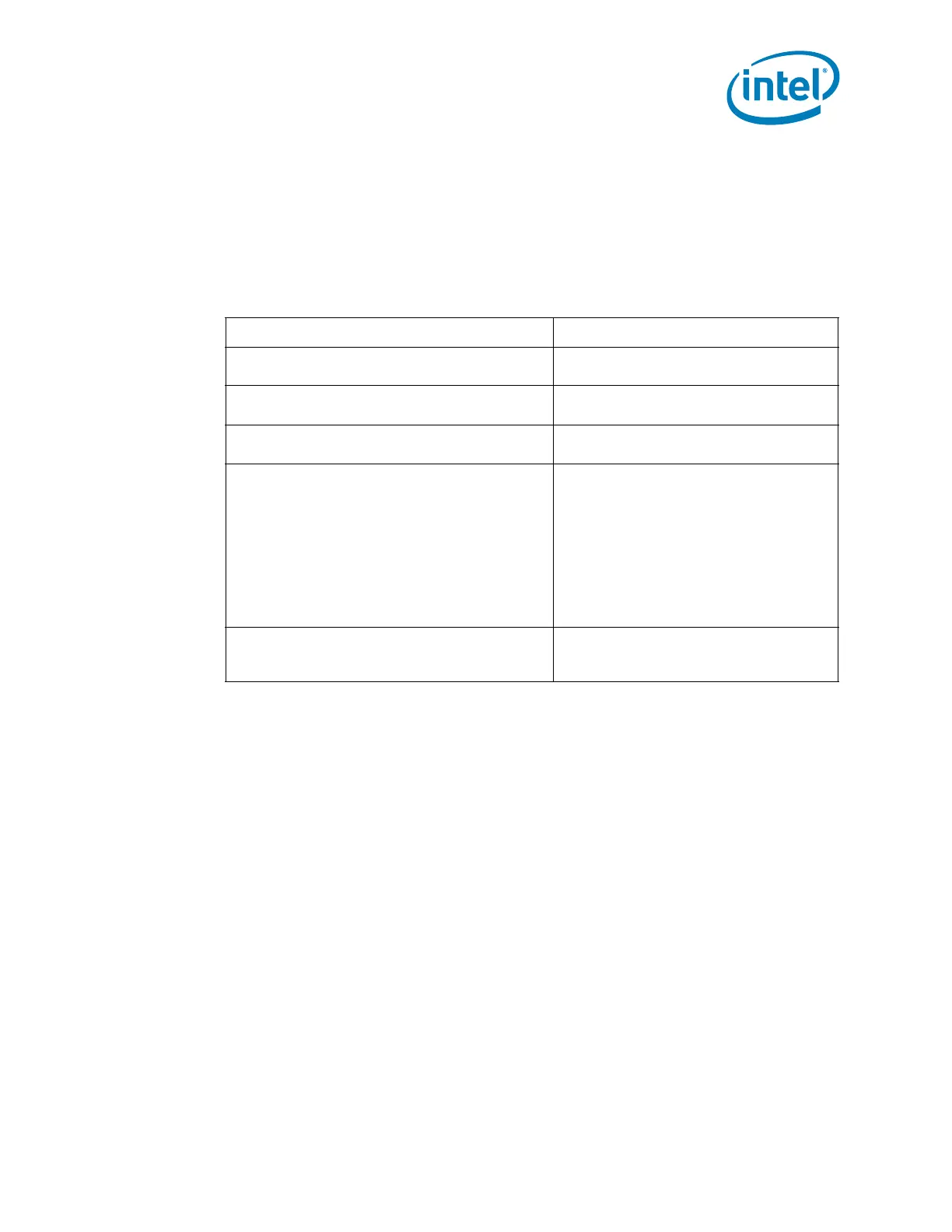

Table 5-22. INIT# Going Active

Cause of INIT3_3V# Going Active Comment

Shutdown special cycle from processor observed

on PCH-processor interconnect.

INIT assertion based on value of Shutdown

Policy Select register (SPS)

PORT92 write, where INIT_NOW (Bit 0) transitions

from a 0 to a 1.

PORTCF9 write, where SYS_RST (Bit 1) was a 0

and RST_CPU (Bit 2) transitions from 0 to 1.

RCIN# input signal goes low. RCIN# is expected

to be driven by the external microcontroller

(KBC).

0 to 1 transition on RCIN# must occur

before the PCH will arm INIT3_3V# to be

generated again.

NOTE: RCIN# signal is expected to be low

during S3, S4, and S5 states.

Transition on the RCIN# signal in

those states (or the transition to

those states) may not necessarily

cause the INIT3_3V# signal to be

generated to the processor.

Processor BIST

To enter BIST, software sets CPU_BIST_EN

bit and then does a full processor reset

using the CF9 register.

Loading...

Loading...