Datasheet 143

Functional Description

Both count and status of the selected counters may be latched simultaneously. This is

functionally the same as issuing two consecutive, separate Read Back commands. If

multiple count and/or status Read Back commands are issued to the same counters

without any intervening reads, all but the first are ignored.

If both count and status of a counter are latched, the first read operation from that

counter returns the latched status, regardless of which was latched first. The next one

or two reads, depending on whether the counter is programmed for one or two type

counts, returns the latched count. Subsequent reads return unlatched count.

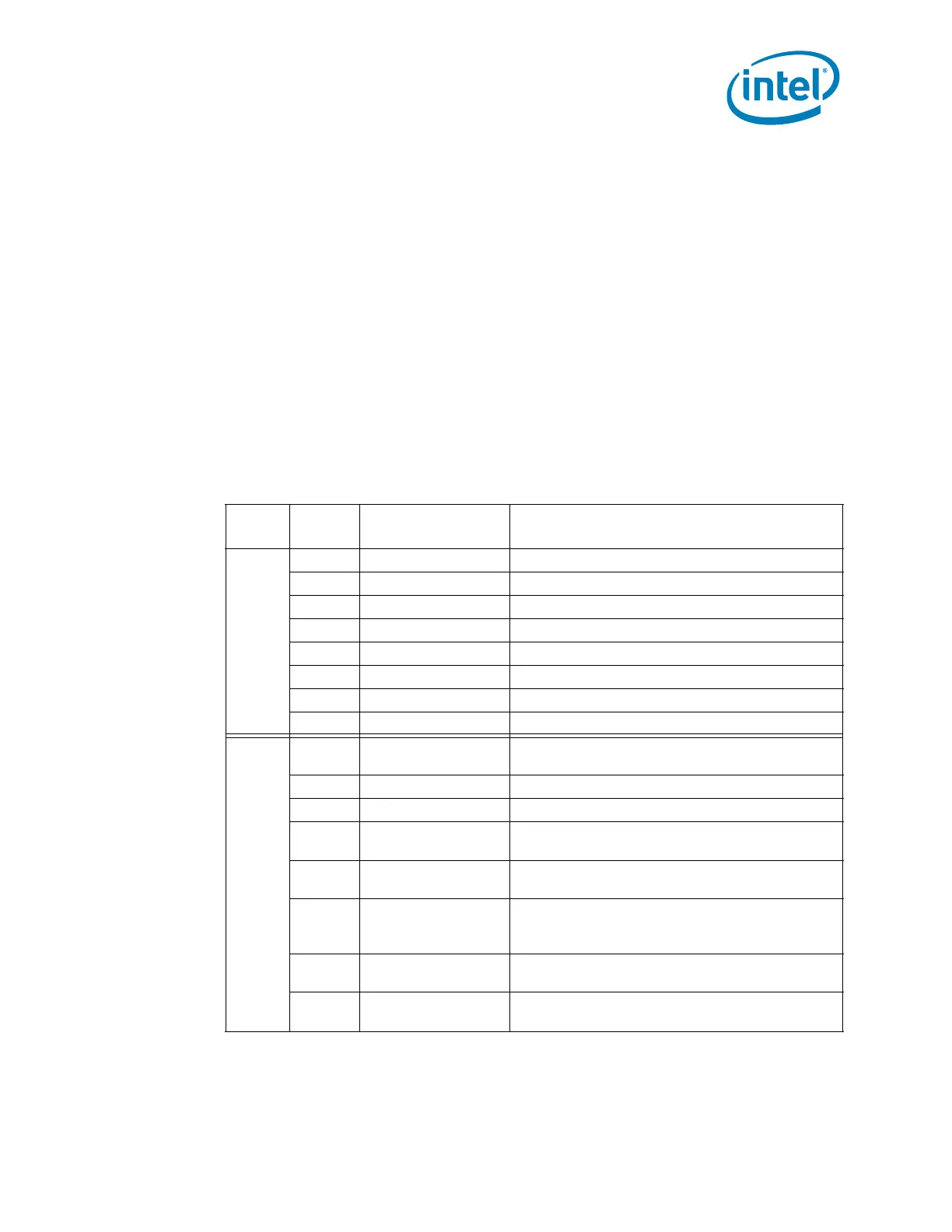

5.8 8259 Interrupt Controllers (PIC) (D31:F0)

The PCH incorporates the functionality of two 8259 interrupt controllers that provide

system interrupts for the ISA compatible interrupts. These interrupts are: system

timer, keyboard controller, serial ports, parallel ports, floppy disk, mouse, and DMA

channels. In addition, this interrupt controller can support the PCI based interrupts, by

mapping the PCI interrupt onto the compatible ISA interrupt line. Each 8259 core

supports eight interrupts, numbered 0–7. Table 5-15 shows how the cores are

connected.

.

The PCH cascades the slave controller onto the master controller through master

controller interrupt input 2. This means there are only 15 possible interrupts for the

PCH PIC.

Table 5-15. Interrupt Controller Core Connections

8259

8259

Input

Typical Interrupt

Source

Connected Pin / Function

Master

0 Internal Internal Timer / Counter 0 output / HPET #0

1 Keyboard IRQ1 using SERIRQ

2 Internal Slave controller INTR output

3 Serial Port A IRQ3 using SERIRQ, PIRQ#

4 Serial Port B IRQ4 using SERIRQ, PIRQ#

5 Parallel Port / Generic IRQ5 using SERIRQ, PIRQ#

6 Floppy Disk IRQ6 using SERIRQ, PIRQ#

7 Parallel Port / Generic IRQ7 using SERIRQ, PIRQ#

Slave

0

Internal Real Time

Clock

Internal RTC / HPET #1

1 Generic IRQ9 using SERIRQ, SCI, TCO, or PIRQ#

2 Generic IRQ10 using SERIRQ, SCI, TCO, or PIRQ#

3Generic

IRQ11 using SERIRQ, SCI, TCO, or PIRQ#, or HPET

#2

4PS/2 Mouse

IRQ12 using SERIRQ, SCI, TCO, or PIRQ#, or HPET

#3

5Internal

State Machine output based on processor FERR#

assertion. May optionally be used for SCI or TCO

interrupt if FERR# not needed.

6SATA

SATA Primary (legacy mode), or using SERIRQ or

PIRQ#

7SATA

SATA Secondary (legacy mode) or using SERIRQ or

PIRQ#

Loading...

Loading...