Functional Description

120 Datasheet

5.2.2.4 SMI/SCI Generation

Interrupts for power management events are not supported on legacy operating

systems. To support power management on non-PCI Express aware operating systems,

PM events can be routed to generate SCI. To generate SCI, MPC.PMCE must be set.

When set, a power management event will cause SMSCS.PMCS (D28:F0/F1/F2/F3/F4/

F5/F6/F7:Offset DCh:Bit 31) to be set.

Additionally, BIOS workarounds for power management can be supported by setting

MPC.PMME (D28:F0/F1/F2/F3/F4/F5/F6/F7:Offset D8h:Bit 0). When this bit is set,

power management events will set SMSCS.PMMS (D28:F0/F1/F2/F3/F4/F5/F6/

F7:Offset DCh:Bit 0), and SMI # will be generated. This bit will be set regardless of

whether interrupts or SCI is enabled. The SMI# may occur concurrently with an

interrupt or SCI.

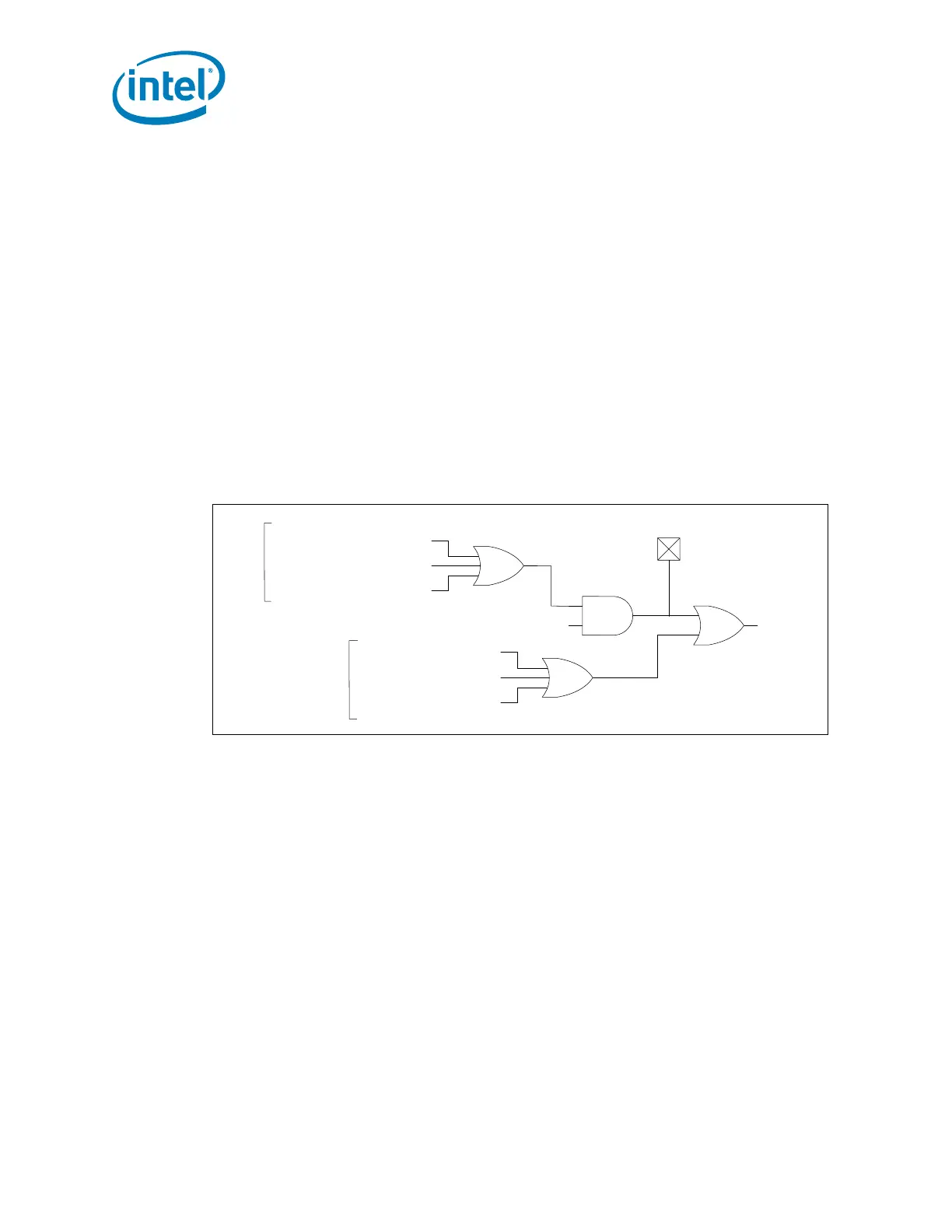

5.2.3 SERR# Generation

SERR# may be generated using two paths – through PCI mechanisms involving bits in

the PCI header, or through PCI Express

*

mechanisms involving bits in the PCI Express

capability structure.

5.2.4 Hot-Plug

Each root port implements a Hot-Plug controller that performs the following:

• Messages to turn on/off/blink LEDs

• Presence and attention button detection

• Interrupt generation

The root port only allows Hot-Plug with modules (such as, ExpressCard*). Edge-

connector based Hot-Plug is not supported.

Figure 5-1. Generation of SERR# to Platform

PSTS.SSE

SERR#

PCICMD.SEE

Secondary Parity Error

Primary Parity Error

Secondary SERR#

Correctable SERR#

Fatal SERR#

Non-Fatal SERR#

PCI

PCI Express

Loading...

Loading...