Functional Description

204 Datasheet

5.18 USB EHCI Host Controllers (D29:F0 and D26:F0)

The PCH contains two Enhanced Host Controller Interface (EHCI) host controllers which

support up to fourteen USB 2.0 high-speed root ports. USB 2.0 allows data transfers up

to 480 Mb/s. USB 2.0 based Debug Port is also implemented in the PCH.

5.18.1 EHC Initialization

The following descriptions step through the expected PCH Enhanced Host Controller

(EHC) initialization sequence in chronological order, beginning with a complete power

cycle in which the suspend well and core well have been off.

5.18.1.1 BIOS Initialization

BIOS performs a number of platform customization steps after the core well has

powered up. Contact your Intel Field Representative for additional PCH BIOS

information.

5.18.1.2 Driver Initialization

See Chapter 4 of the Enhanced Host Controller Interface Specification for Universal

Serial Bus, Revision 1.0.

5.18.1.3 EHC Resets

In addition to the standard PCH hardware resets, portions of the EHC are reset by the

HCRESET bit and the transition from the D3

HOT

device power management state to the

D0 state. The effects of each of these resets are:

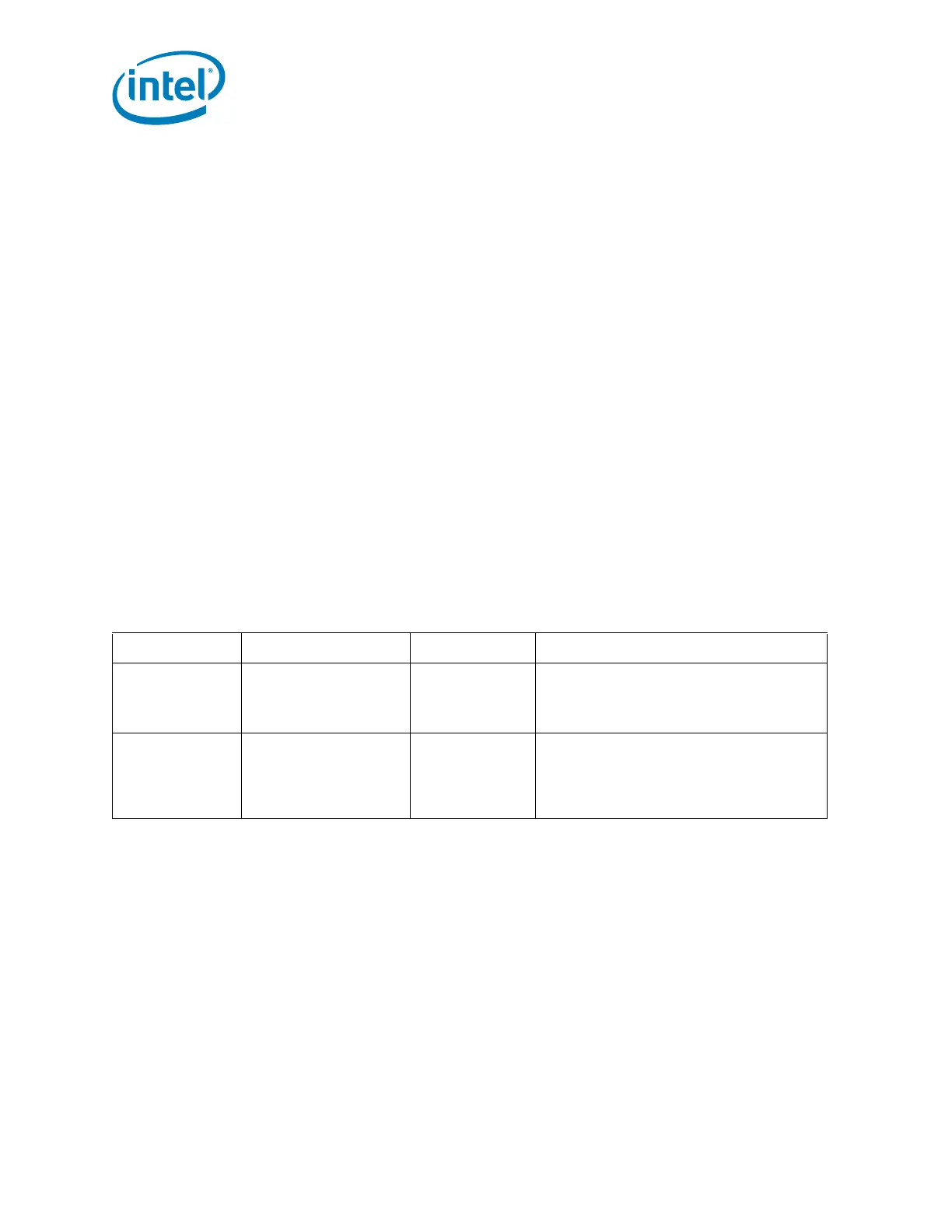

If the detailed register descriptions give exceptions to these rules, those exceptions

override these rules. This summary is provided to help explain the reasons for the reset

policies.

5.18.2 Data Structures in Main Memory

See Section 3 and Appendix B of the Enhanced Host Controller Interface Specification

for Universal Serial Bus, Revision 1.0 for details.

Reset Does Reset Does not Reset Comments

HCRESET bit set.

Memory space registers

except Structural

Parameters (which is

written by BIOS).

Configuration

registers.

The HCRESET must only affect registers that

the EHCI driver controls. PCI Configuration

space and BIOS-programmed parameters

cannot be reset.

Software writes

the Device Power

State from D3

HOT

(11b) to D0 (00b).

Core well registers

(except BIOS-

programmed registers).

Suspend well

registers; BIOS-

programmed core

well registers.

The D3-to-D0 transition must not cause

wake information (suspend well) to be lost.

It also must not clear BIOS-programmed

registers because BIOS may not be invoked

following the D3-to-D0 transition.

Loading...

Loading...