Functional Description

164 Datasheet

In systems using the APIC, the SCI can be routed to interrupts 9, 10, 11, 20, 21, 22, or

23. The interrupt polarity changes depending on whether it is on an interrupt shareable

with a PIRQ or not (see Section 13.1.3). The interrupt remains asserted until all SCI

sources are removed.

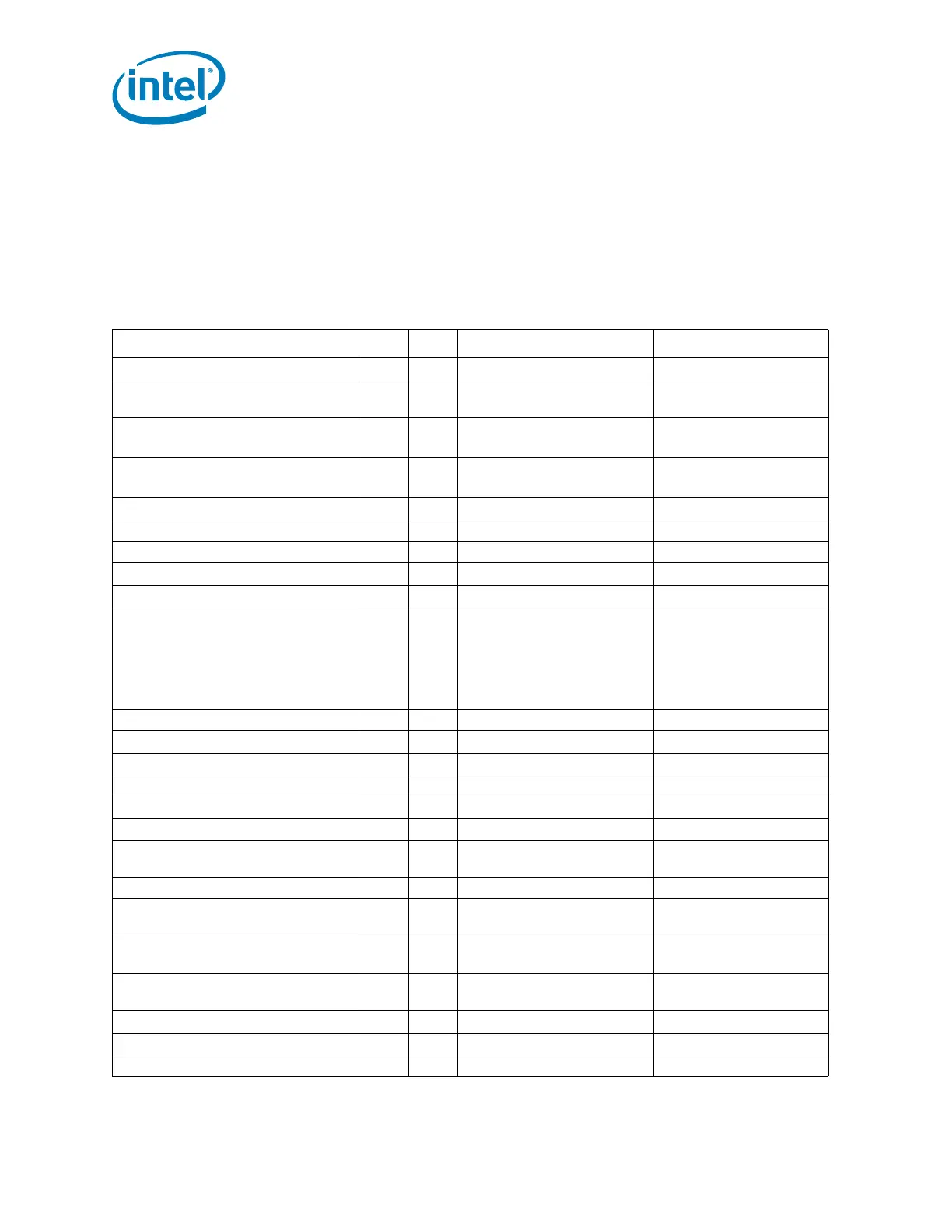

Table 5-27 shows which events can cause an SMI and SCI. Note that some events can

be programmed to cause either an SMI or SCI. The usage of the event for SCI (instead

of SMI) is typically associated with an ACPI-based system. Each SMI or SCI source has

a corresponding enable and status bit.

Table 5-27. Causes of SMI and SCI (Sheet 1 of 2)

Cause SCI SMI Additional Enables Where Reported

PME# Yes Yes PME_EN=1 PME_STS

PME_B0 (Internal, Bus 0, PME-

Capable Agents)

Yes Yes PME_B0_EN=1 PME_B0_STS

PCI Express* PME Messages Yes Yes

PCI_EXP_EN=1

(Not enabled for SMI)

PCI_EXP_STS

PCI Express Hot Plug Message Yes Yes

HOT_PLUG_EN=1

(Not enabled for SMI)

HOT_PLUG_STS

Power Button Press Yes Yes PWRBTN_EN=1 PWRBTN_STS

Power Button Override (Note 7) Yes No None PRBTNOR_STS

RTC Alarm Yes Yes RTC_EN=1 RTC_STS

Ring Indicate Yes Yes RI_EN=1 RI_STS

ACPI Timer overflow (2.34 sec.) Yes Yes TMROF_EN=1 TMROF_STS

Any GPI[15:0] Yes Yes

GPI[x]_Route=10;

GPI[x]_EN=1

(SCI)

GPI[x]_Route=01;

ALT_GPI_SMI[x]_EN=1

(SMI)

GPI[x]_STS

ALT_GPI_SMI[x]_STS

GPIO[27] Yes Yes GP27_EN=1 GP27_STS

TCO SCI Logic Yes No TCOSCI_EN=1 TCOSCI_STS

TCO SCI message from processor Yes No none CPUSCI_STS

TCO SMI Logic No Yes TCO_EN=1 TCO_STS

TCO SMI

– No Yes none NEWCENTURY_STS

TCO SMI

– TCO TIMEROUT No Yes none TIMEOUT

TCO SMI

– OS writes to TCO_DAT_IN

register

No Yes none OS_TCO_SMI

TCO SMI

– Message from processor No Yes none CPUSMI_STS

TCO SMI

– NMI occurred (and NMIs

mapped to SMI)

No Yes NMI2SMI_EN=1 NMI2SMI_STS

TCO SMI

– INTRUDER# signal goes

active

No Yes INTRD_SEL=10 INTRD_DET

TCO SMI

– Change of the BIOSWE

(D31:F0:DCh, Bit 0) bit from 0 to 1

No Yes BLE=1 BIOSWR_STS

TCO SMI

– Write attempted to BIOS No Yes BIOSWE=1 BIOSWR_STS

BIOS_RLS written to Yes No GBL_EN=1 GBL_STS

GBL_RLS written to No Yes BIOS_EN=1 BIOS_STS

Loading...

Loading...