Datasheet 165

Functional Description

NOTES:

1. SCI_EN must be 1 to enable SCI, except for BIOS_RLS. SCI_EN must be 0 to enable SMI.

2. SCI can be routed to cause interrupt 9:11 or 20:23 (20:23 only available in APIC mode).

3. GBL_SMI_EN must be 1 to enable SMI.

4. EOS must be written to 1 to re-enable SMI for the next 1.

5. The PCH must have SMI fully enabled when the PCH is also enabled to trap cycles. If SMI is not enabled in

conjunction with the trap enabling, then hardware behavior is undefined.

6. Only GPI[15:0] may generate an SMI or SCI.

7. When a power button override first occurs, the system will transition immediately to S5. The SCI will only

occur after the next wake to S0 if the residual status bit (PRBTNOR_STS) is not cleared prior to setting

SCI_EN.

8. GBL_STS being set will cause an SCI, even if the SCI_EN bit is not set. Software must take great care not

to set the BIOS_RLS bit (which causes GBL_STS to be set) if the SCI handler is not in place.

5.13.4.1 PCI Express* SCI

PCI Express ports and the processor (using DMI) have the ability to cause PME using

messages. When a PME message is received, the PCH will set the PCI_EXP_STS bit. If

the PCI_EXP_EN bit is also set, the PCH can cause an SCI using the GPE1_STS register.

5.13.4.2 PCI Express* Hot-Plug

PCI Express has a Hot-Plug mechanism and is capable of generating a SCI using the

GPE1 register. It is also capable of generating an SMI. However, it is not capable of

generating a wake event.

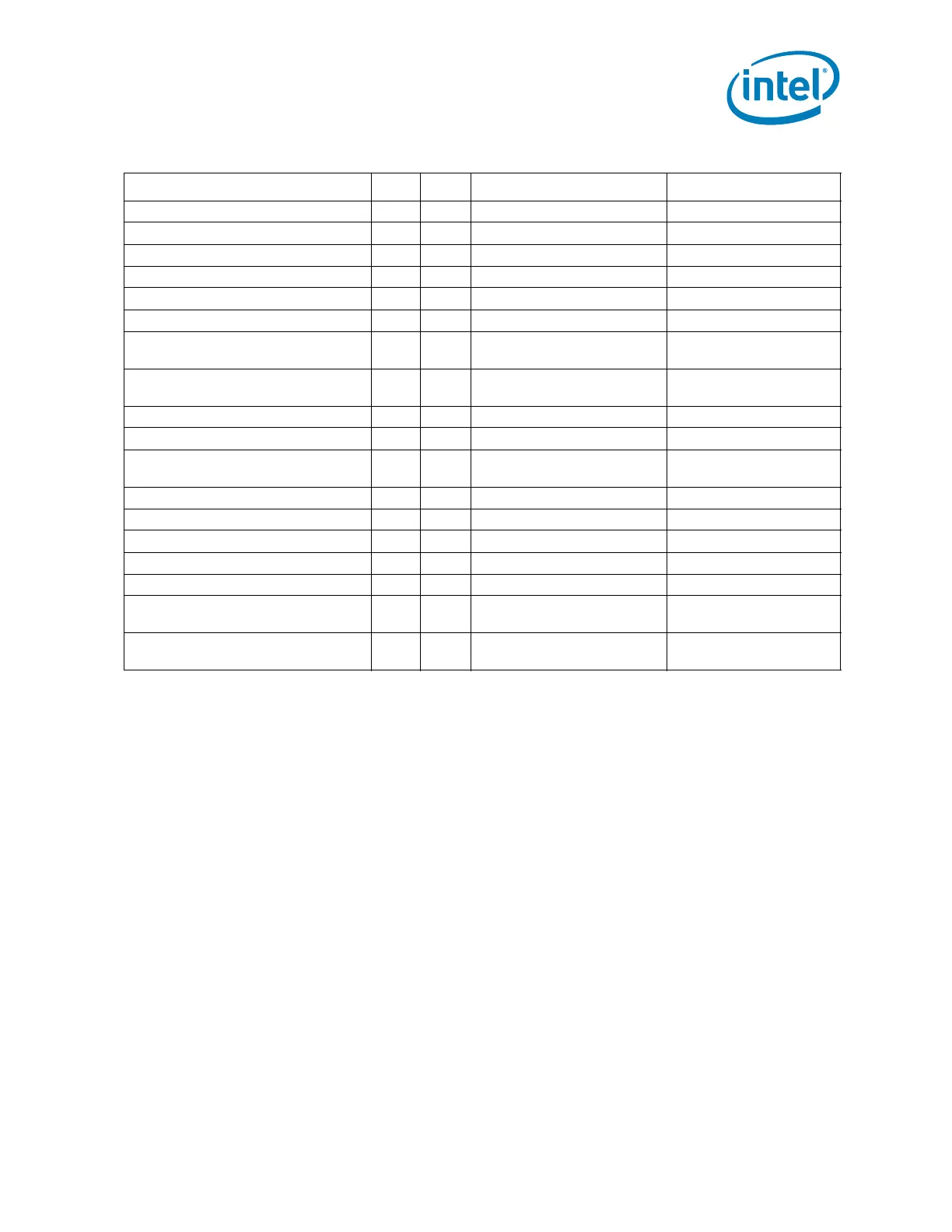

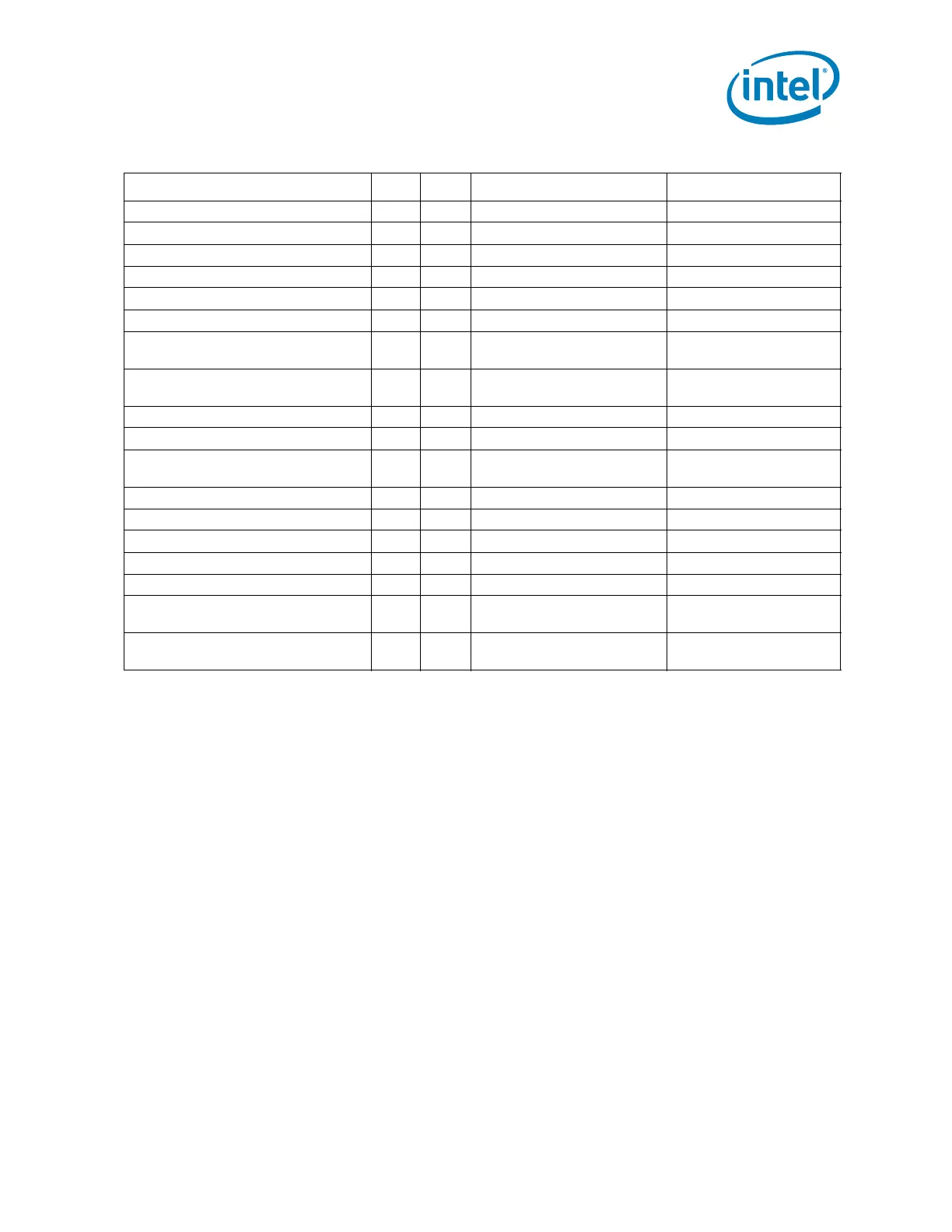

Write to B2h register No Yes APMC_EN = 1 APM_STS

Periodic timer expires No Yes PERIODIC_EN=1 PERIODIC_STS

64 ms timer expires No Yes SWSMI_TMR_EN=1 SWSMI_TMR_STS

Enhanced USB Legacy Support Event No Yes LEGACY_USB2_EN = 1 LEGACY_USB2_STS

Enhanced USB Intel Specific Event No Yes INTEL_USB2_EN = 1 INTEL_USB2_STS

Serial IRQ SMI reported No Yes none SERIRQ_SMI_STS

Device monitors match address in its

range

No Yes none DEVTRAP_STS

SMBus Host Controller No Yes

SMB_SMI_EN

Host Controller Enabled

SMBus host status reg.

SMBus Slave SMI message No Yes none SMBUS_SMI_STS

SMBus SMBALERT# signal active No Yes none SMBUS_SMI_STS

SMBus Host Notify message received No Yes HOST_NOTIFY_INTREN

SMBUS_SMI_STS

HOST_NOTIFY_STS

(Mobile Only) BATLOW# assertion Yes Yes BATLOW_EN=1 BATLOW_STS

Access microcontroller 62h/66h No Yes MCSMI_EN MCSMI_STS

SLP_EN bit written to 1 No Yes SMI_ON_SLP_EN=1 SMI_ON_SLP_EN_STS

SPI Command Completed No Yes None SPI_SMI_STS

Software Generated GPE Yes Yes SWGPE=1 SWGPE_STS

USB Per-Port Registers Write Enable

bit changes to 1

No Yes

USB2_EN=1,

Write_Enable_SMI_Enable=1

USB2_STS, Write Enable

Status

GPIO Lockdown Enable bit changes

from ‘1’ to ‘0’

No Yes GPIO_UNLOCK_SMI_EN=1 GPIO_UNLOCK_SMI_STS

Table 5-27. Causes of SMI and SCI (Sheet 2 of 2)

Cause SCI SMI Additional Enables Where Reported

Loading...

Loading...