Signal Description

56 Datasheet

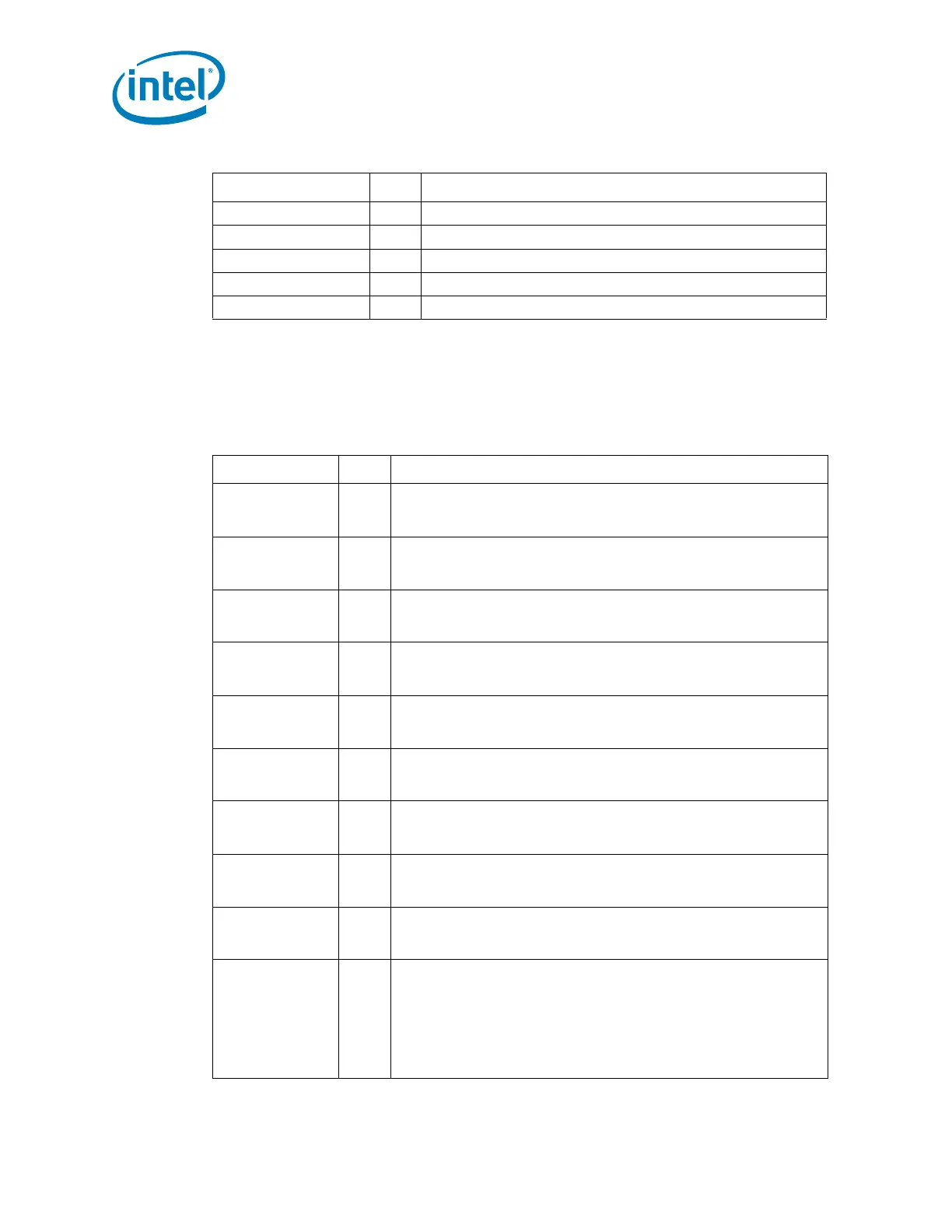

2.3 PCI Interface

Note: PCI Interface is not available, except for specific signal exceptions called out below.

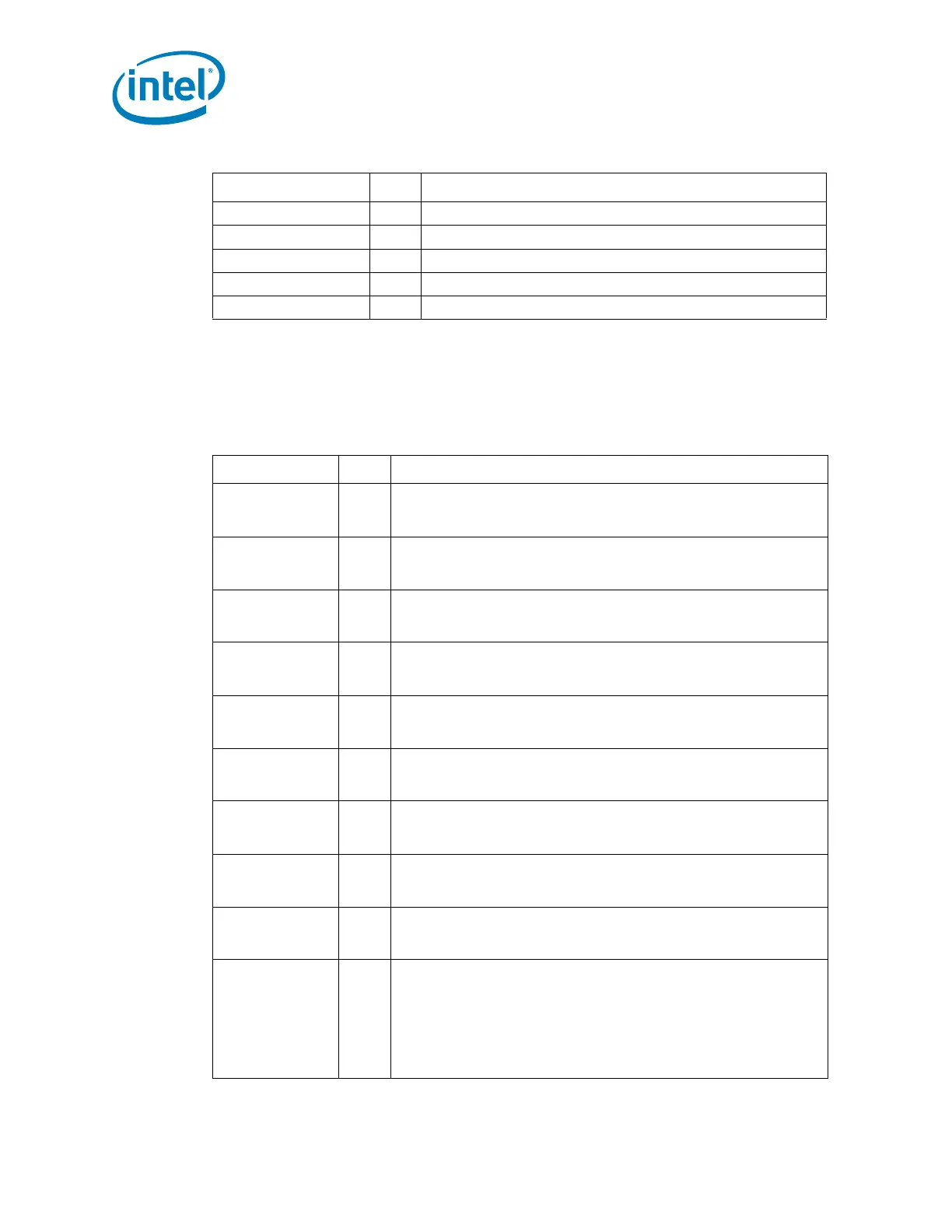

PERp6, PERn6 I PCI Express Differential Receive Pair 6

PETp7, PETn7 O PCI Express Differential Transmit Pair 7

PERp7, PERn7 I PCI Express Differential Receive Pair 7

PETp8, PETn8 O PCI Express Differential Transmit Pair 8

PERp8, PERn8 I PCI Express Differential Receive Pair 8

Table 2-3. PCI Interface Signals (Sheet 1 of 2)

Name Type Description

AD[31:0] (not

available in

mobile)

I/O PCI Address/Data: Reserved.

C/BE[3:0]# (not

available in

mobile)

I/O Bus Command and Byte Enables: Reserved.

DEVSEL# (not

available in

mobile)

I/O Device Select: Reserved.

FRAME# (not

available in

mobile)

I/O Cycle Frame: Reserved.

IRDY# (not

available in

mobile)

I/O Initiator Ready: Reserved.

TRDY# (not

available in

mobile)

I/O Target Ready: Reserved.

STOP# (not

available in

mobile)

I/O Stop: Reserved.

PAR (not

available in

mobile)

I/O Calculated/Checked Parity: Reserved.

PERR# (not

available in

mobile)

I/O Parity Error: Reserved.

REQ0# (not

available in

mobile)

REQ1#/ GPIO50

REQ2#/ GPIO52

REQ3#/GPIO54

I

PCI Requests: REQ functionality is Reserved.

REQ[3:1]# pins can instead be used as GPIO.

NOTES:

1. REQ[3:0]# functionality not available.

2. An external pull-up resistor to Vcc3_3 is required when a pin

is not used as a GPIO (that is, a pull-up is required when not

used).

Table 2-2. PCI Express* Signals (Sheet 2 of 2)

Name Type Description

Loading...

Loading...