Datasheet 303

Electrical Characteristics

NOTES:

1. V

DI

= | USBPx[P] – USBPx[N]

2. Includes VDI range

3. Applies to Low-Speed/High-Speed USB

4. PCI Express mVdiff p-p = 2*|PETp[x] – PETn[x]|

5. SATA Vdiff, RX (VIMAX10/MIN10) is measured at the SATA connector on the receiver side

(generally, the motherboard connector), where SATA mVdiff p-p = 2*|SATA[x]RXP –

SATA[x]RXN|

6. VccRTC is the voltage applied to the VccRTC well of the PCH. When the system is in a G3

state, this is generally supplied by the coin cell battery, but for S5 and greater, this is

generally VccSus3_3.

7. CL_Vref = 0.12*(VccSus3_3)

8. This is an AC characteristic that represents transient values for these signals.

9. Applies to High-Speed USB 2.0.

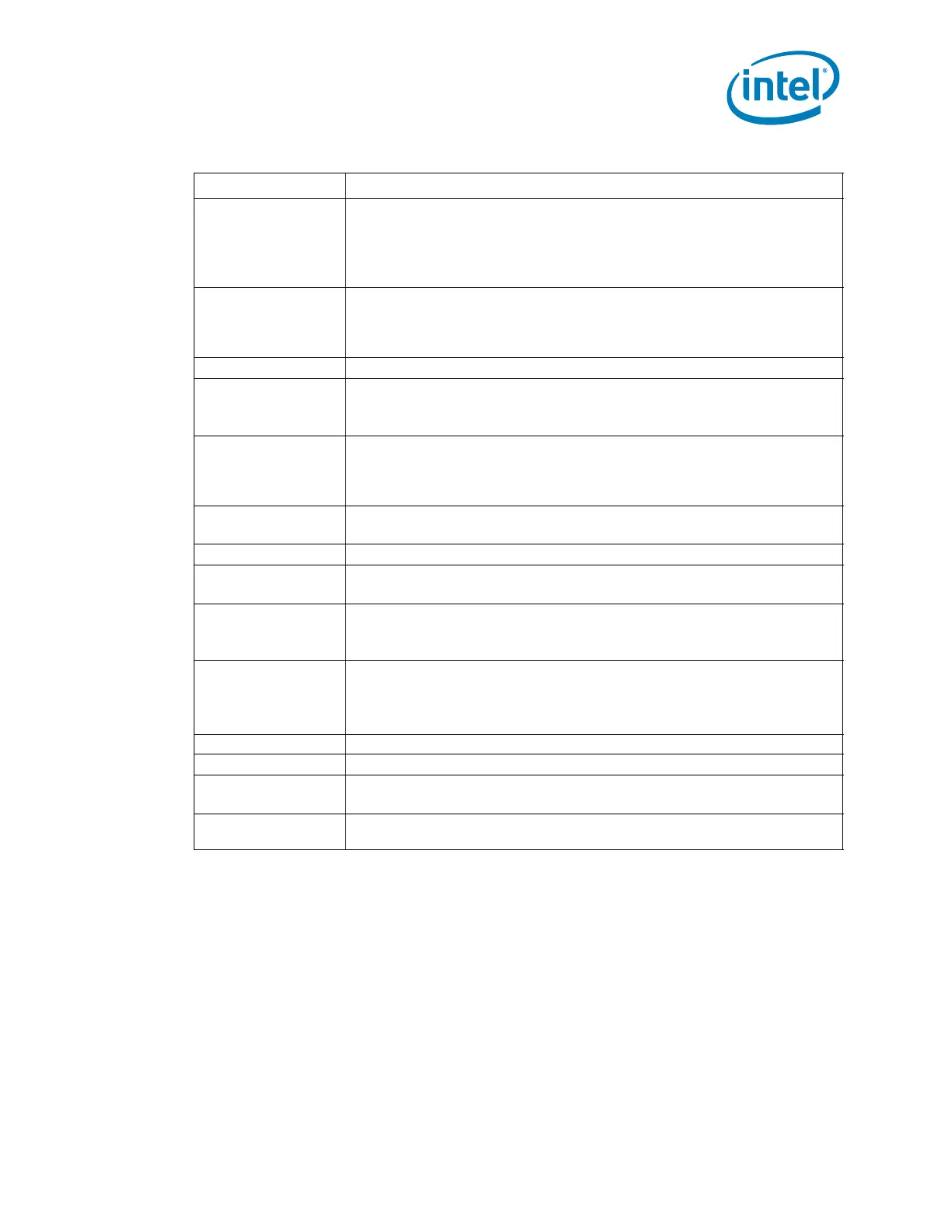

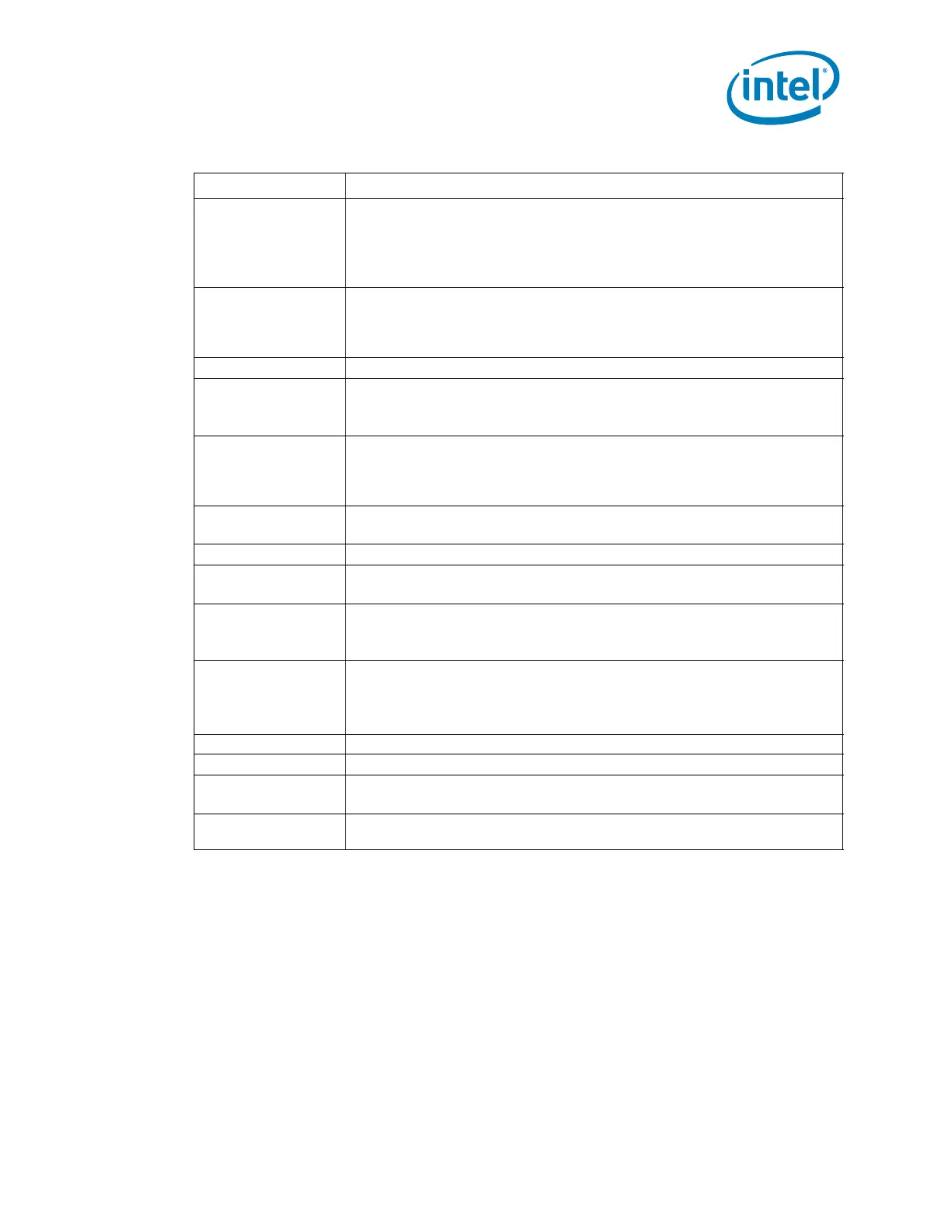

VIH11/VIL11

Intel High Definition Audio Signals: HDA_SDIN[3:0] (3.3V Mode)

Strap Signals: HDA_SDO, HDA_SYNC (Strap purposes only)

GPIO Signals: GPIO13

NOTE: See VIL_HDA/VIH_HDA for High Definition Audio Low Voltage Mode

VIH12 (Absolute

Maximum) / VIL12

(Absolute Minimum) /

Vclk_in_cross(abs)

Clock Signals: CLKIN_DMI_[P,N], CLKIN_DOT96[P,N], CLKIN_SATA_[P,N]]

VIH13/VIL13

Miscellaneous Signals: RTCRST#

VIH14/VIL14

Power Management Signals: PWROK, RSMRST#, DPWROK

System Management Signals: INTRUDER#

Miscellaneous Signals: INTVRMEN, SRTCRST#

VIH15/VIL15

Digital Display Control Signals: CRT_DDC_CLK, CRT_DDC_DATA

SDVO_CTRLCLK, SDVO_CTRLDATA, DDPC_CTRLCLK, DDPC_CTRLDATA,

DDPD_CTRLCLK, DDPD_CTRLDATA

Mobile only: L_BKLTEN, L_BKLTCTL, L_DDC_CLK, L_DDC_DATA

VIH16/VIL16

Processor Interface: RCIN#

Power Management Signals: SYS_PWROK, APWROK

VIH_CL/VIL_CL

Controller Link: CL_CLK1, CL_DATA1

VDI / VCM / VSE

(5V Tolerant)

USB Signals: USBP[13:0][P,N] (Low-speed and Full-speed)

V

HSSQ

/ V

HSDSC

/

V

HSCM

(5V Tolerant)

USB Signals: USBP[13:0][P,N] (in High-speed Mode)

VIH_HDA / VIL_HDA

Intel

®

High Definition Audio Signals: HDA_SDIN[3:0]

Strap Signals: HDA_SDO, HDA_SYNC (Strap purposes only)

NOTE: Only applies when running in Low Voltage Mode (1.5 V)

VIH_FDI/VIL_FDI

Intel

®

Flexible Display Interface Signals: FDI_RX[P,N][7:0]

VAUX-Diff-P-P

Digital Display Port Aux Signal (Receiving Side): DDP[D:B]_AUX[P,N]

VIH_XTAL25/

VIL_XTAL25

25MHz Crystal Input

XTAL25_IN

VIMIN17-Gen3i/

VIMAX17-Gen3i

SATA Signals: SATA[5:0]RX[P,N] (6.0 Gb/s internal SATA)

Table 8-7. DC Characteristic Input Signal Association (Sheet 2 of 2)

Symbol Associated Signals

Loading...

Loading...