Datasheet 427

PCI-to-PCI Bridge Registers (D30:F0)

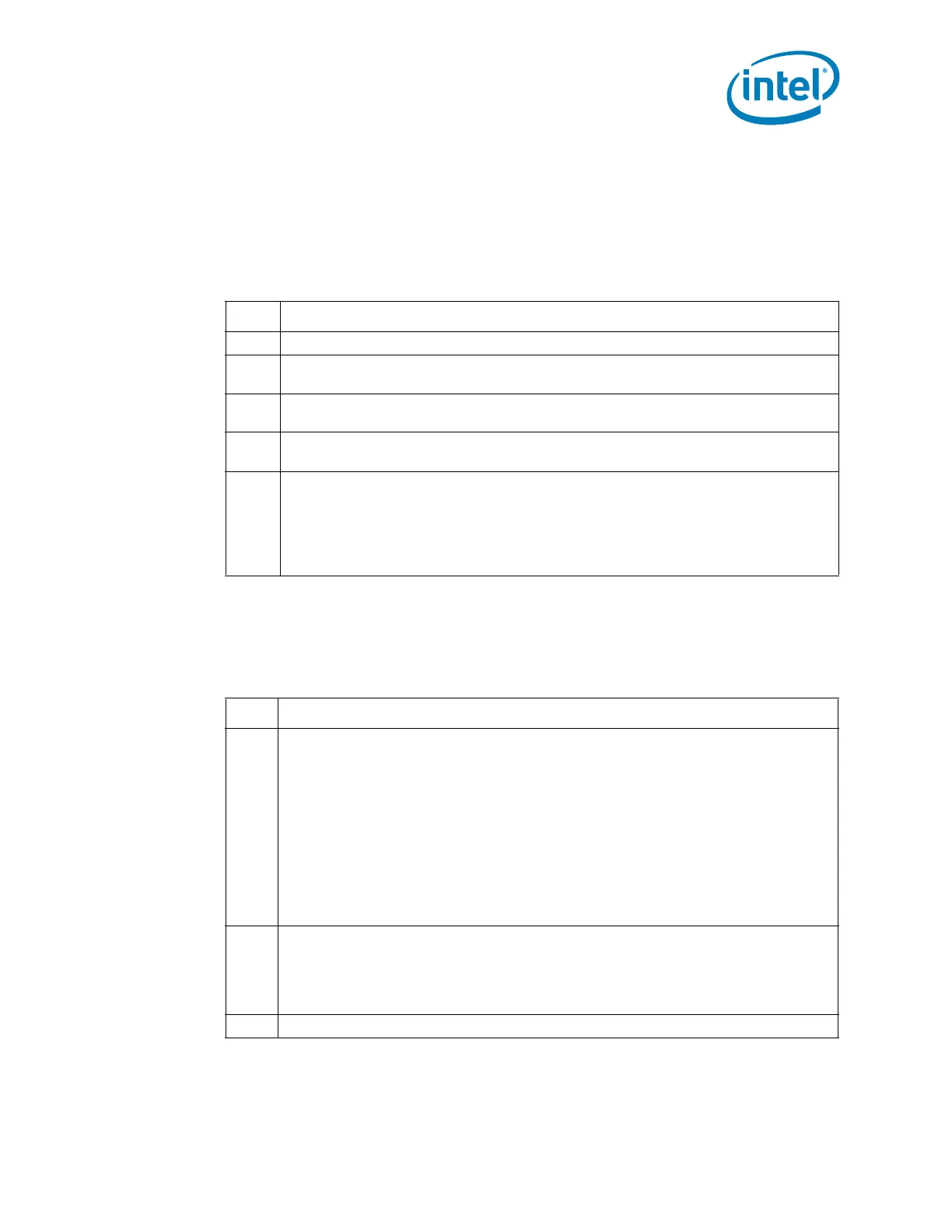

11.1.20 SPDH—Secondary PCI Device Hiding Register

(PCI-PCI—D30:F0)

Offset Address: 40h–41h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

This register allows software to hide the PCI devices, either plugged into slots or on the

motherboard.

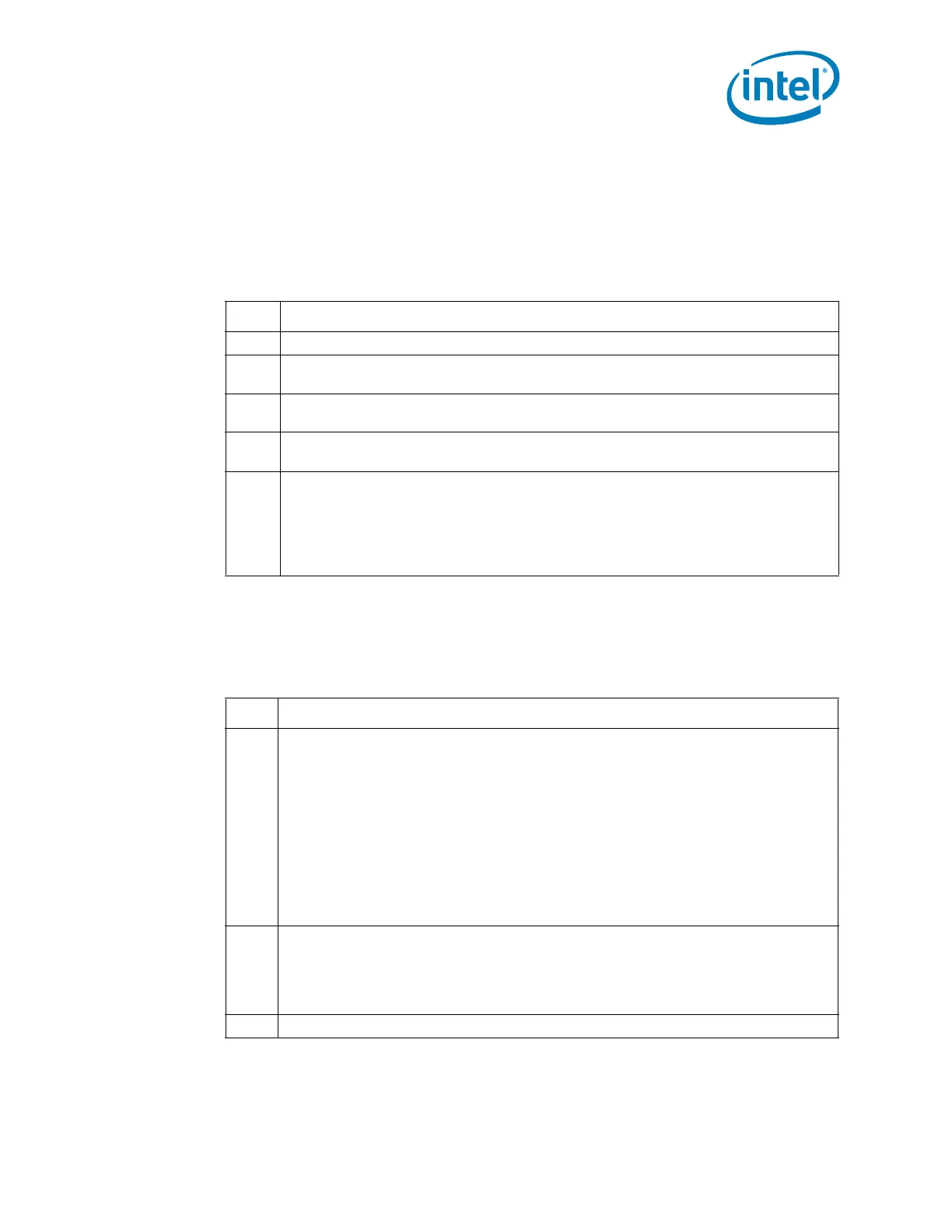

11.1.21 DTC—Delayed Transaction Control Register

(PCI-PCI—D30:F0)

Offset Address: 44h–47h Attribute: R/W

Default Value: 00000000h Size: 32 bits

Bit Description

15:4 Reserved

3

Hide Device 3 (HD3) — R/W, RO. Same as bit 0 of this register, except for device 3

(AD[19])

2

Hide Device 2 (HD2) — R/W, RO. Same as bit 0 of this register, except for device 2

(AD[18])

1

Hide Device 1 (HD1) — R/W, RO. Same as bit 0 of this register, except for device 1

(AD[17])

0

Hide Device 0 (HD0) — R/W, RO.

0 = The PCI configuration cycles for this slot are not affected.

1 = The PCH hides device 0 on the PCI bus. This is done by masking the IDSEL

(keeping it low) for configuration cycles to that device. Since the device will not see

its IDSEL go active, it will not respond to PCI configuration cycles and the

processor will think the device is not present. AD[16] is used as IDSEL for device 0.

Bit Description

31

Discard Delayed Transactions (DDT) — R/W.

0 = Logged delayed transactions are kept.

1 = The PCH PCI bridge will discard any delayed transactions it has logged. This

includes transactions in the pending queue, and any transactions in the active

queue, whether in the hard or soft DT state. The prefetchers will be disabled and

return to an idle state.

NOTES:If a transaction is running on PCI at the time this bit is set, that transaction will

continue until either the PCI master disconnects (by deasserting FRAME#) or

the PCI bridge disconnects (by asserting STOP#). This bit is cleared by the PCI

bridge when the delayed transaction queues are empty and have returned to an

idle state. Software sets this bit and polls for its completion.

30

Block Delayed Transactions (BDT) — R/W.

0 = Delayed transactions accepted

1 = The PCH PCI bridge will not accept incoming transactions which will result in

delayed transactions. It will blindly retry these cycles by asserting STOP#. All

postable cycles (memory writes) will still be accepted.

29:8 Reserved

Loading...

Loading...