Datasheet 429

PCI-to-PCI Bridge Registers (D30:F0)

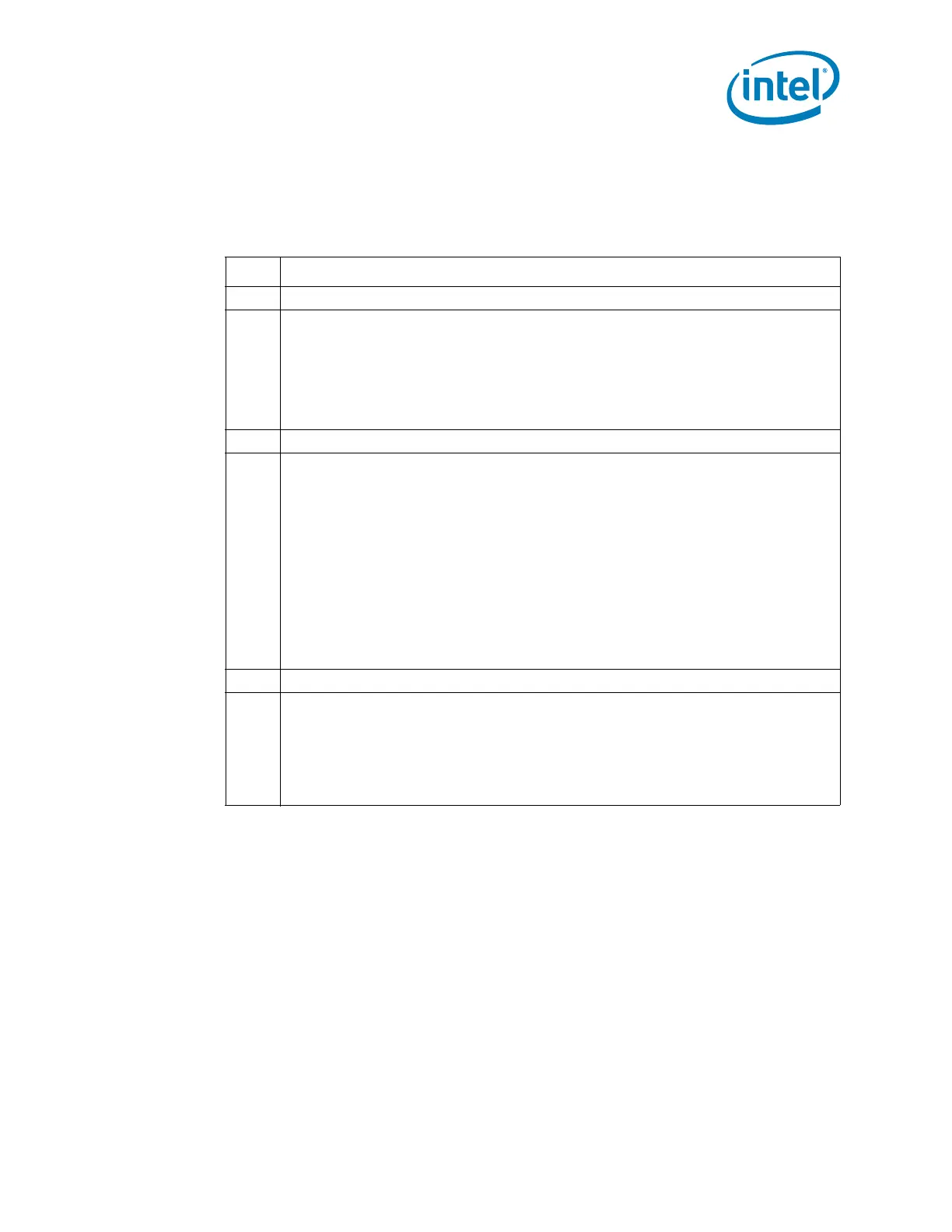

11.1.22 BPS—Bridge Proprietary Status Register

(PCI-PCI—D30:F0)

Offset Address: 48h–4Bh Attribute: R/WC, RO

Default Value: 00000000h Size: 32 bits

Bit Description

31:17 Reserved

16

PERR# Assertion Detected (PAD) — R/WC. This bit is set by hardware whenever the

PERR# pin is asserted on the rising edge of PCI clock. This includes cases in which the

chipset is the agent driving PERR#. It remains asserted until cleared by software

writing a 1 to this location. When enabled by the PERR#-to-SERR# Enable bit (in the

Bridge Policy Configuration register), a 1 in this bit can generate an internal SERR# and

be a source for the NMI logic.

This bit can be used by software to determine the source of a system problem.

15:7 Reserved

6:4

Number of Pending Transactions (NPT) — RO. This read-only indicator tells debug

software how many transactions are in the pending queue. Possible values are:

000 = No pending transaction

001 = 1 pending transaction

010 = 2 pending transactions

011 = 3 pending transactions

100 = 4 pending transactions

101 = 5 pending transactions

110–111 = Reserved

NOTE: This field is not valid if DTC.MDT (offset 44h:bits 7:6) is any value other than

‘00’.

3:2 Reserved

1:0

Number of Active Transactions (NAT) — RO. This read-only indicator tells debug

software how many transactions are in the active queue. Possible values are:

00 = No active transactions

01 = 1 active transaction

10 = 2 active transactions

11 = Reserved

Loading...

Loading...