Datasheet 431

PCI-to-PCI Bridge Registers (D30:F0)

11.1.24 SVCAP—Subsystem Vendor Capability Register

(PCI-PCI—D30:F0)

Offset Address: 50h–51h Attribute: RO

Default Value: 000Dh Size: 16 bits

7

Subtractive Decode Policy (SDP) — R/W.

0 = The PCI bridge always forwards memory and I/O cycles that are not claimed by any

other device on the backbone (primary interface) to the PCI bus (secondary

interface).

1 = The PCI bridge will not claim and forward memory or I/O cycles at all unless the

corresponding Space Enable bit is set in the Command register.

NOTE: The Boot BIOS Destination Selection strap can force the BIOS accesses to PCI.

6

PERR#-to-SERR# Enable (PSE) — R/W. When this bit is set, a 1 in the PERR#

Assertion status bit (in the Bridge Proprietary Status register) will result in an internal

SERR# assertion on the primary side of the bridge (if also enabled by the SERR#

Enable bit in the primary Command register). SERR# is a source of NMI.

5

Secondary Discard Timer Testmode (SDTT) — R/W.

0 = The secondary discard timer expiration will be defined in BCTRL.SDT (D30:F0:3E,

bit 9)

1 = The secondary discard timer will expire after 128 PCI clocks.

4:3 Reserved

2

Peer Decode Enable (PDE) — R/W.

0 = The PCI bridge assumes that all memory cycles target main memory, and all I/O

cycles are not claimed.

1 = The PCI bridge will perform peer decode on any memory or I/O cycle from PCI that

falls outside of the memory and I/O window registers

1 Reserved

0

Received Target Abort SERR# Enable (RTAE) — R/W. When set, the PCI bridge will

report SERR# when PSTS.RTA (D30:F0:06 bit 12) or SSTS.RTA (D30:F0:1E bit 12) are

set, and CMD.SEE (D30:F0:04 bit 8) is set.

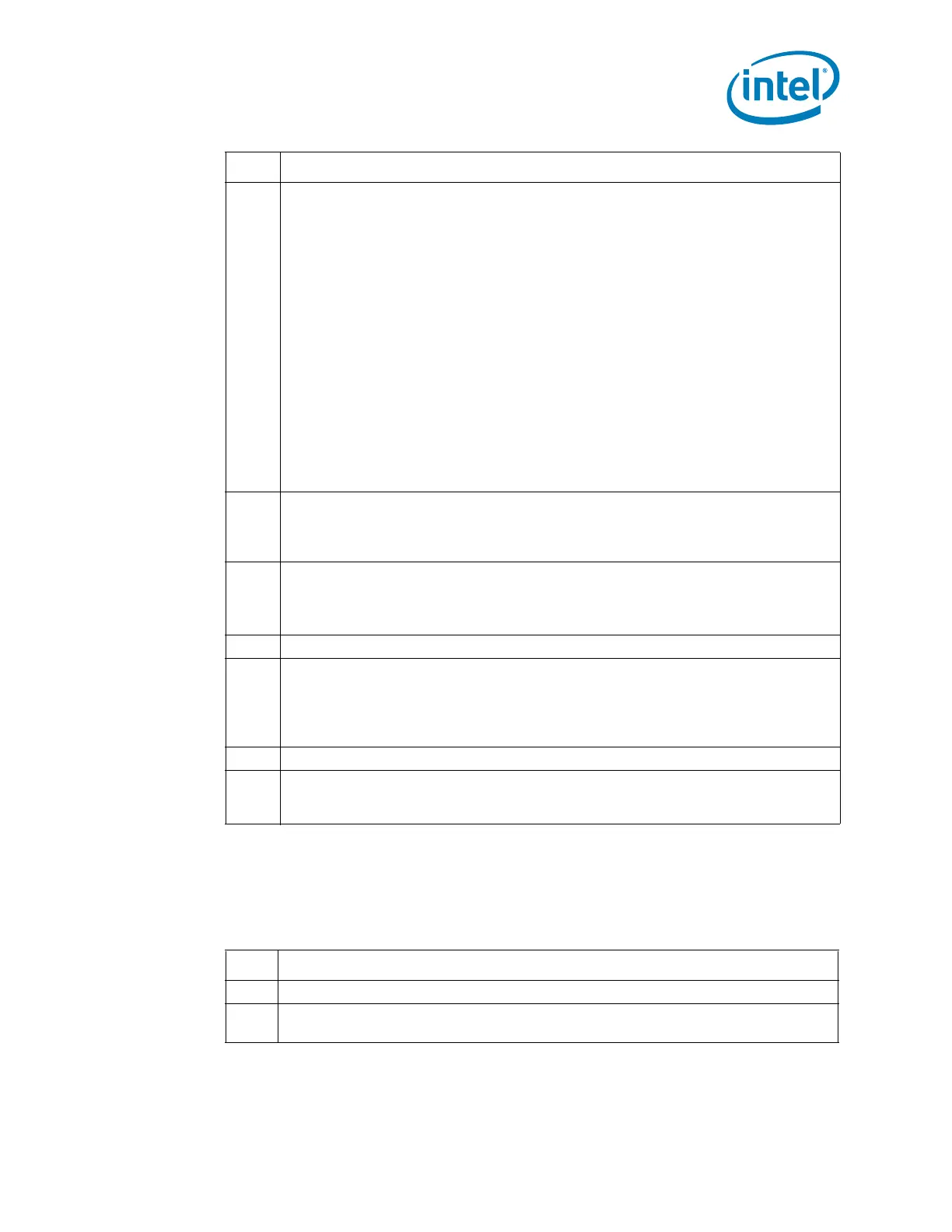

Bit Description

CMD.MSE BPC.SDP Range Forwarding Policy

00Don’t Care

Forward unclaimed

cycles

0 1 Don’t Care Forwarding Prohibited

1XWithin range

Positive decode and

forward

1XOutside

Subtractive decode &

forward

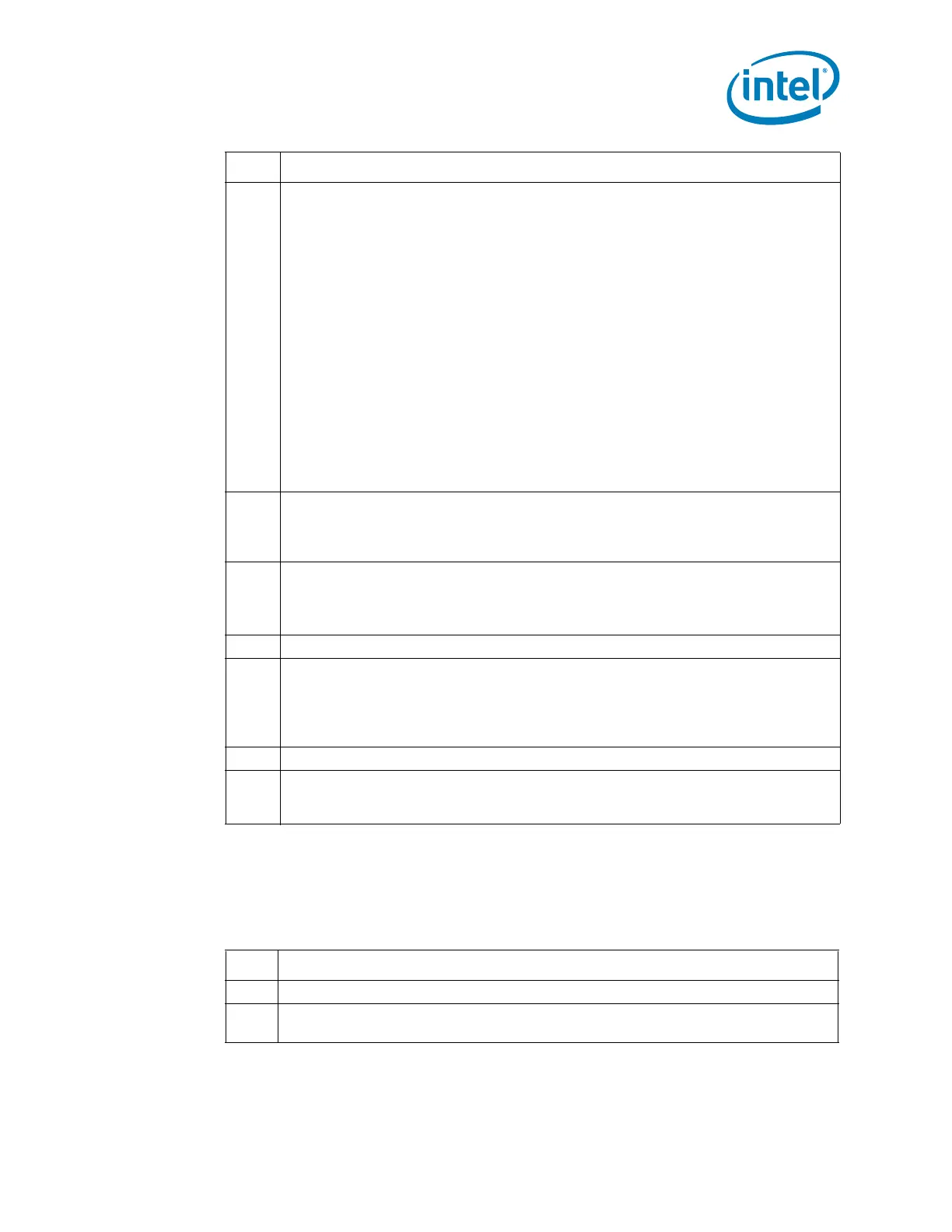

Bit Description

15:8 Next Capability (NEXT) — RO. Value of 00h indicates this is the last item in the list.

7:0

Capability Identifier (CID) — RO. Value of 0Dh indicates this is a PCI bridge

subsystem vendor capability.

Loading...

Loading...