Datasheet 509

LPC Interface Bridge Registers (D31:F0)

13.8.1.3 GEN_PMCON_3—General PM Configuration 3 Register

(PM—D31:F0)

Offset Address: A4h Attribute: R/W, R/WC

Default Value: 4206h Size: 16-bit

Lockable: No Usage: ACPI, Legacy

Power Well: RTC, SUS

1

SYS_PWROK Failure (SYSPWR_FLR) — R/WC.

0 = This bit will be cleared only be software writing a 1 back to the bit or by SUS well

power loss.

1 = This bit will be set any time SYS_PWROK drops unexpectedly when the system was

in S0 or S1 state.

0

PWROK Failure (PWROK_FLR) — R/WC.

0 = This bit will be cleared only be software writing a 1 back to the bit or by SUS well

power loss.

1 = This bit will be set any time PWROK goes low when the system was in S0 or S1

state.

NOTE: See Chapter 5.13.10.3 for more details about the PWROK pin functionality.

Bit Description

Bit Description

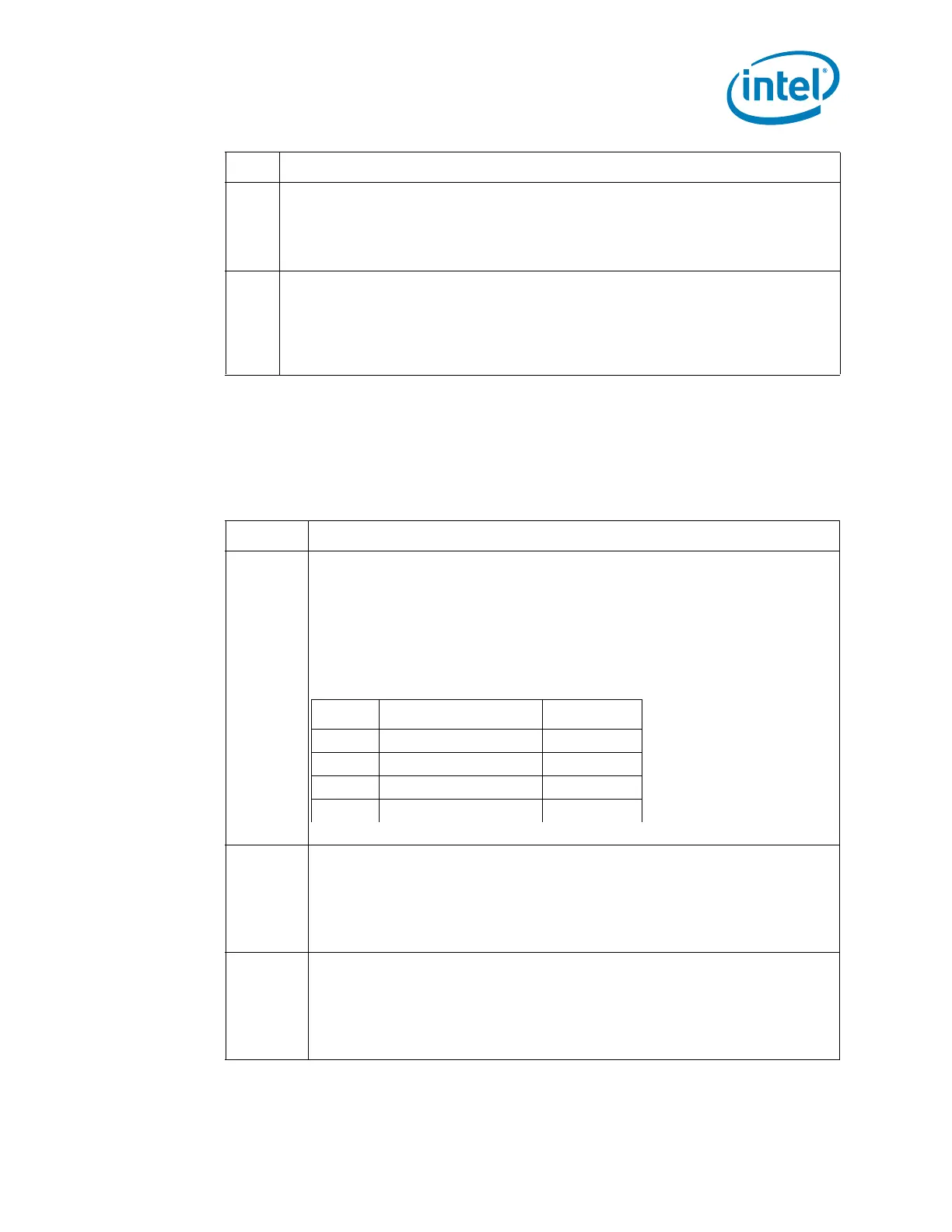

15

PME B0 S5 Disable (PME_B0_S5_DIS)— R/W. When set to 1, this bit blocks

wake events from PME_B0_STS in S5, regardless of the state of PME_B0_EN.

When cleared (default), wake events from PME_B0_STS are allowed in S5 if

PME_B0_EN = 1.

Wakes from power states other than S5 are not affected by this policy bit.

The net effect of setting PME_B0_S5_DIS = '1' is described by the truth table

below:

Y = Wake; N = Don't wake; B0 = PME_B0_EN; OV = WOL Enable Override

This bit is cleared by the RTCRST# pin.

14

SUS Well Power Failure (SUS_PWR_FLR) — R/WC.

0 = Software writes a 1 to this bit to clear it.

1 = This bit is set to '1' whenever SUS well power is lost, as indicated by RSMRST#

assertion.

This bit is in the SUS well, and defaults to '1' based on RSMRST# assertion (not

cleared by any type of reset).

13

WOL Enable Override (WOL_EN_OVRD) — R/W.

0 = WOL policies are determined by PMEB0 enable bit and appropriate LAN status

bits

1 = Enable appropriately configured integrated LAN to wake the system in S5 only

regardless of the value in the PME_B0_EN bit in the GPE0_EN register.

This bit is cleared by the RTCRST# pin.

B0/OV S1/S3/S4 S5

00 N N

01 N Y (LAN only)

11 Y (all PME B0 sources) Y (LAN only)

10 Y (all PME B0 sources) N

Loading...

Loading...