Datasheet 613

SATA Controller Registers (D31:F2)

14.4.2.12 PxSERR—Port [5:0] Serial ATA Error Register (D31:F2)

Address Offset: Port 0: ABAR + 130h Attribute: R/WC

Port 1: ABAR + 1B0h

Port 2: ABAR + 230h (if port available; see Section 1.3)

Port 3: ABAR + 2B0h (if port available; see Section 1.3)

Port 4: ABAR + 330h

Port 5: ABAR + 3B0h

Default Value: 00000000h Size: 32 bits

Bits 26:16 of this register contain diagnostic error information for use by diagnostic

software in validating correct operation or isolating failure modes. Bits 11:0 contain

error information used by host software in determining the appropriate response to the

error condition. If one or more of bits 11:8 of this register are set, the controller will

stop the current transfer.

3:0

Device Detection Initialization (DET) — R/W. Controls the PCH’s device detection

and interface initialization.

All other values reserved.

When this field is written to a 1h, the PCH initiates COMRESET and starts the

initialization process. When the initialization is complete, this field shall remain 1h until

set to another value by software.

This field may only be changed to 1h or 4h when PxCMD.ST is 0. Changing this field

while the PCH is running results in undefined behavior.

NOTE: It is permissible to implement any of the Serial ATA defined behaviors for

transmission of COMRESET when DET=1h.

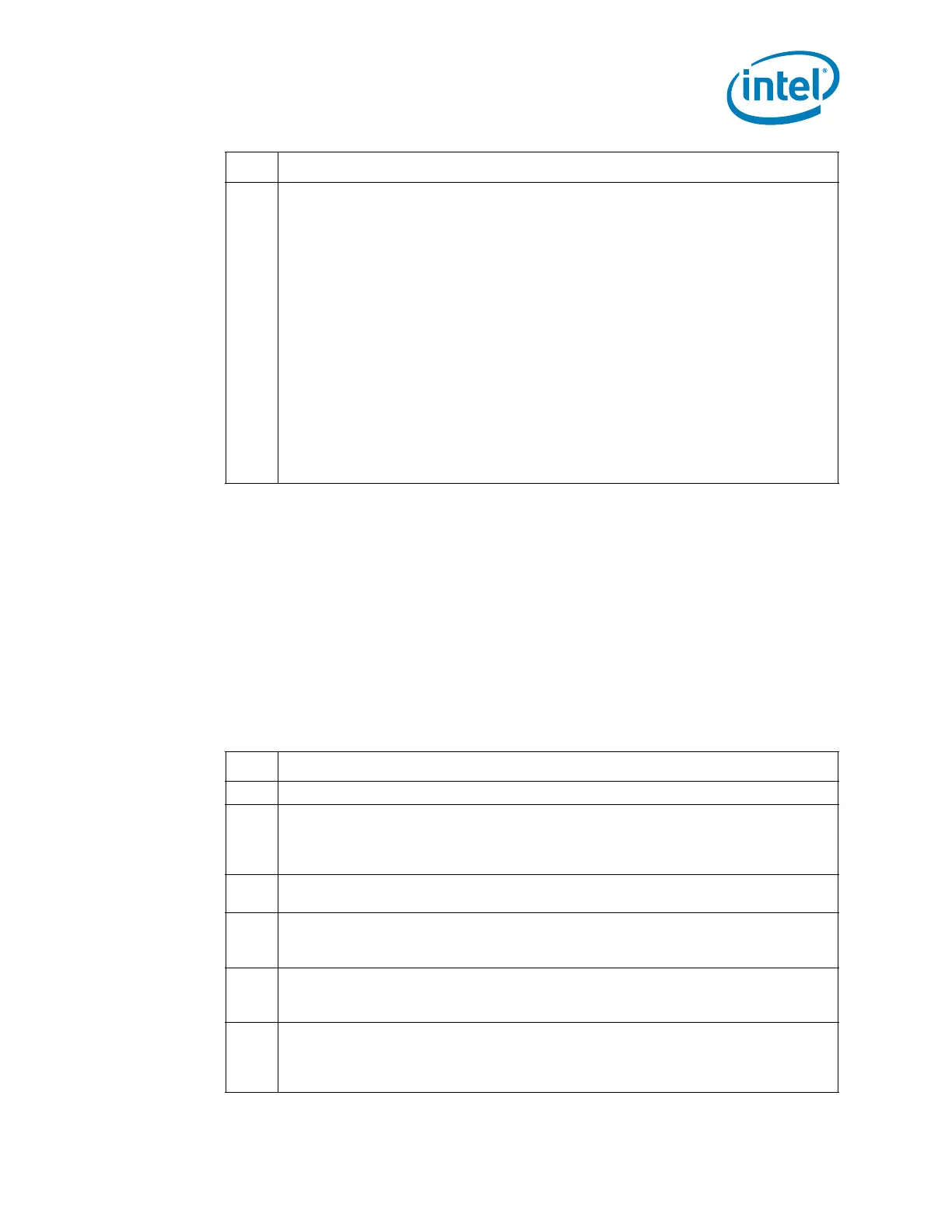

Bit Description

Value Description

0h No device detection or initialization action requested

1h

Perform interface communication initialization sequence to

establish communication. This is functionally equivalent to a hard

reset and results in the interface being reset and communications

re-initialized

4h Disable the Serial ATA interface and put Phy in offline mode

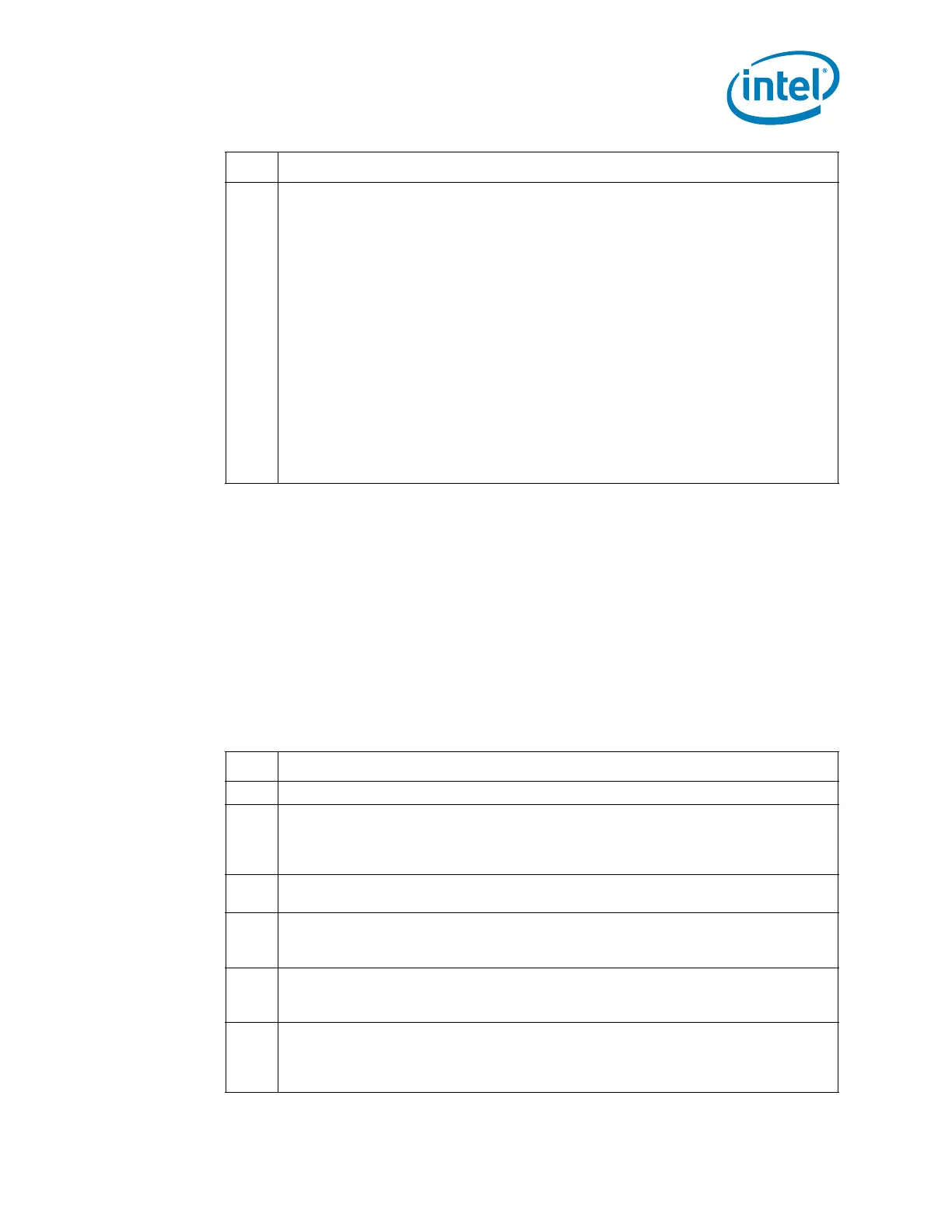

Bit Description

31:27 Reserved

26

Exchanged (X) — R/WC. When set to 1, this bit indicates that a change in device

presence has been detected since the last time this bit was cleared. This bit shall

always be set to 1 anytime a COMINIT signal is received. This bit is reflected in the

P0IS.PCS bit.

25

Unrecognized FIS Type (F) — R/WC. Indicates that one or more FISs were received

by the Transport layer with good CRC, but had a type field that was not recognized.

24

Transport state transition error (T) — R/WC. Indicates that an error has occurred in

the transition from one state to another within the Transport layer since the last time

this bit was cleared.

23

Transport state transition error (T) — R/WC. Indicates that an error has occurred in

the transition from one state to another within the Transport layer since the last time

this bit was cleared.

22

Handshake (H) — R/WC. Indicates that one or more R_ERR handshake response was

received in response to frame transmission. Such errors may be the result of a CRC

error detected by the recipient, a disparity or 8b/10b decoding error, or other error

condition leading to a negative handshake on a transmitted frame.

Loading...

Loading...