Datasheet 711

Integrated Intel

®

High Definition Audio Controller Registers

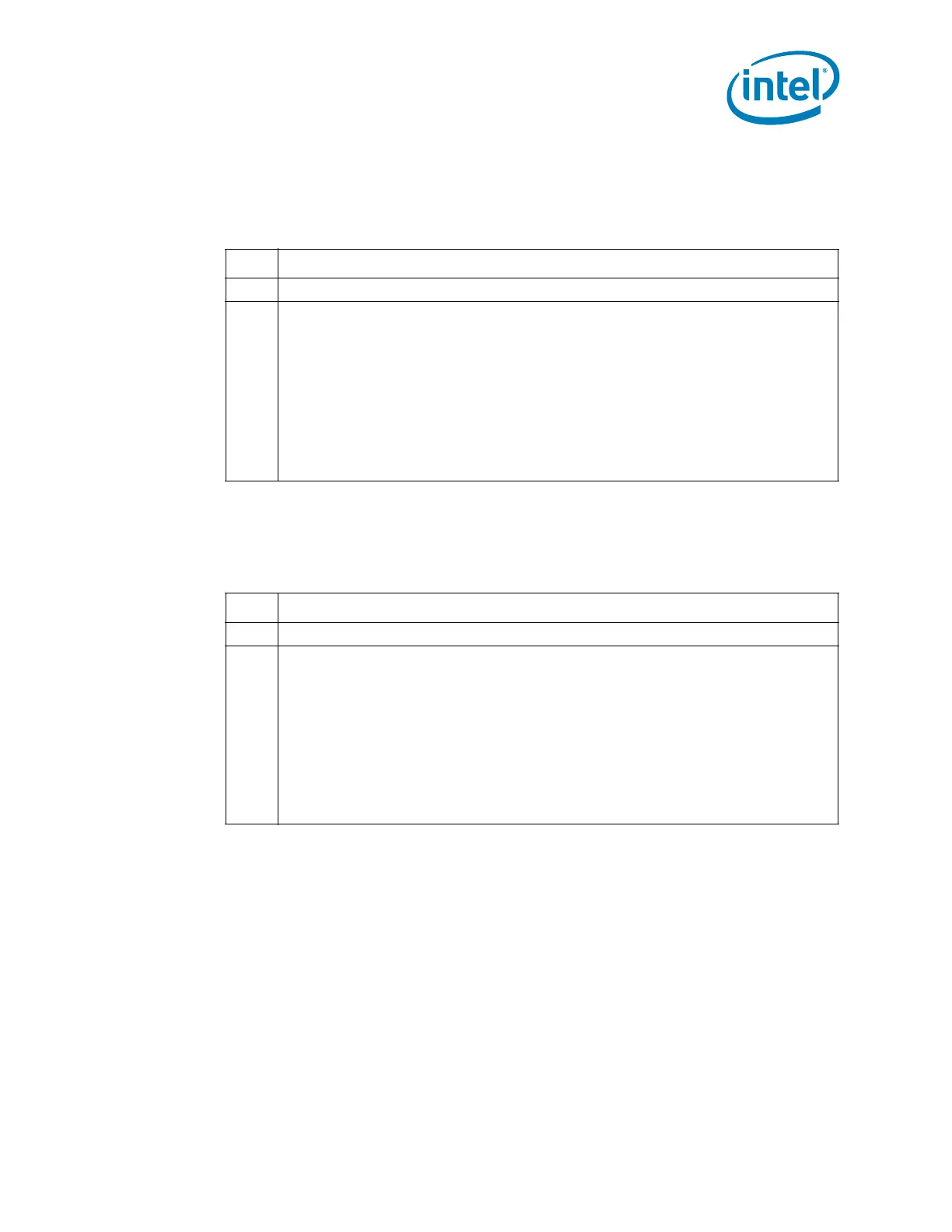

17.1.2.4 OUTPAY—Output Payload Capability Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address:HDBAR + 04h Attribute: RO

Default Value: 003Ch Size: 16 bits

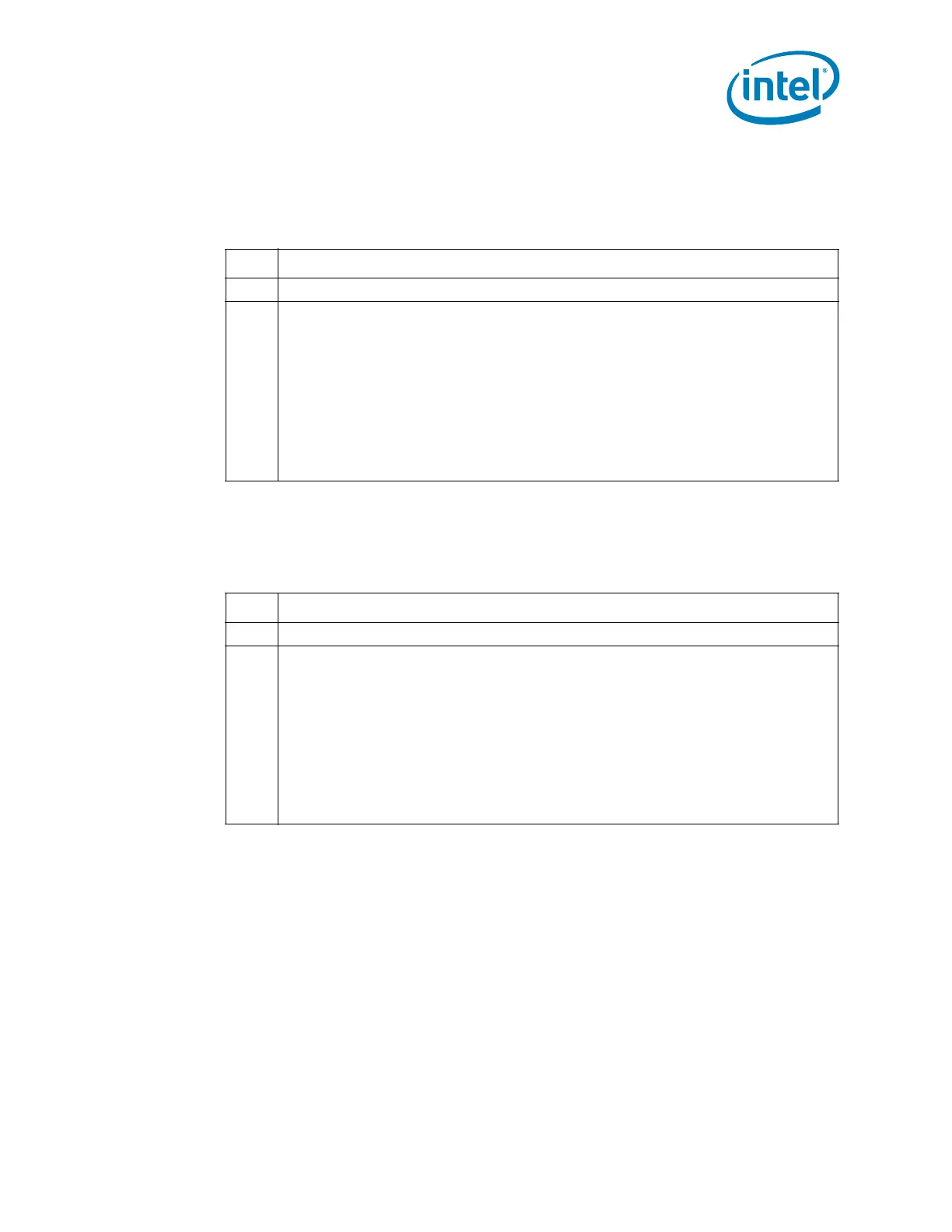

17.1.2.5 INPAY—Input Payload Capability Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address:HDBAR + 06h Attribute: RO

Default Value: 001Dh Size: 16 bits

Bit Description

15:7 Reserved.

6:0

Output Payload Capability — RO. Hardwired to 3Ch indicating 60 word payload.

This field indicates the total output payload available on the link. This does not include

bandwidth used for command and control. This measurement is in 16-bit word

quantities per 48 MHz frame. The default link clock of 24.000 MHz (the data is double

pumped) provides 1000 bits per frame, or 62.5 words in total. 40 bits are used for

command and control, leaving 60 words available for data payload.

00h = 0 word

01h = 1 word payload.

.....

FFh = 256 word payload.

Bit Description

15:7 Reserved.

6:0

Input Payload Capability — RO. Hardwired to 1Dh indicating 29 word payload.

This field indicates the total output payload available on the link. This does not include

bandwidth used for response. This measurement is in 16-bit word quantities per

48 MHz frame. The default link clock of 24.000 MHz provides 500 bits per frame, or

31.25 words in total. 36 bits are used for response, leaving 29 words available for data

payload.

00h = 0 word

01h = 1 word payload.

.....

FFh = 256 word payload.

Loading...

Loading...