SMBus Controller Registers (D31:F3)

740 Datasheet

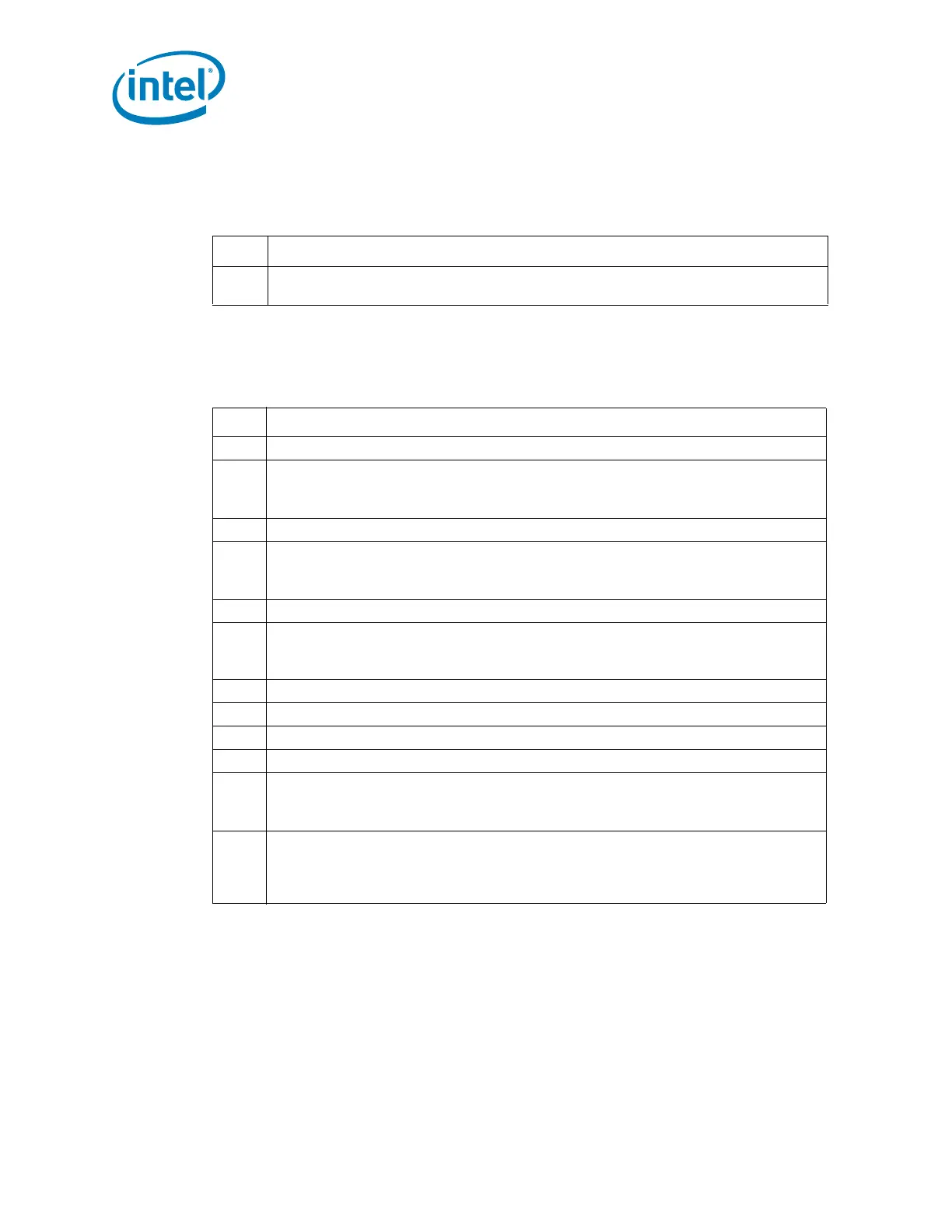

18.1.2 DID—Device Identification Register (SMBus—D31:F3)

Address: 02h–03h Attribute: RO

Default Value: See bit description Size: 16 bits

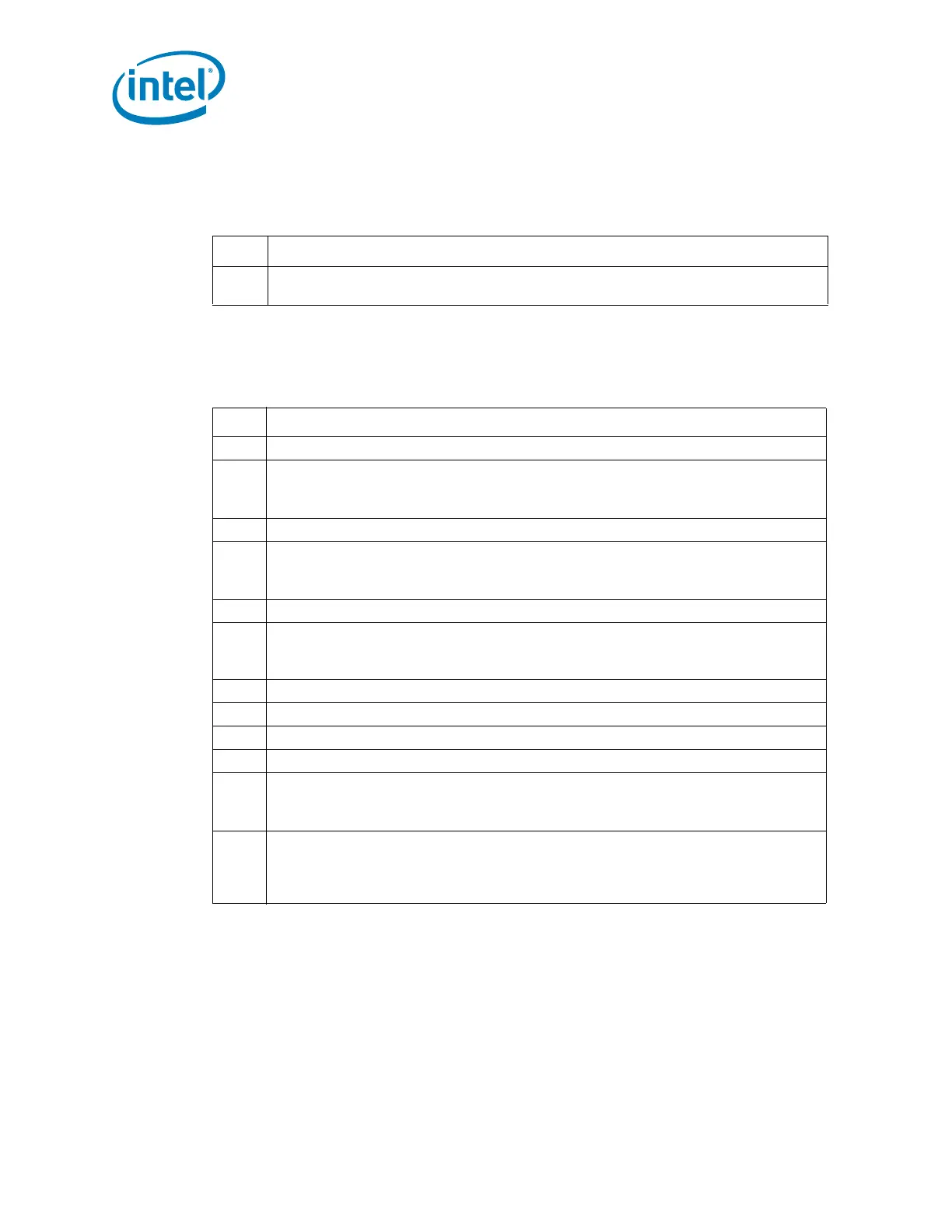

18.1.3 PCICMD—PCI Command Register (SMBus—D31:F3)

Address: 04h–05h Attributes: RO, R/W

Default Value: 0000h Size: 16 bits

Bit Description

15:0

Device ID — RO. This is a 16-bit value assigned to the PCH SMBus controller. See the

Intel

®

6 Series Chipset Specification Update for the value of the DID Register.

Bit Description

15:11 Reserved

10

Interrupt Disable — R/W.

0 = Enable

1 = Disables SMBus to assert its PIRQB# signal.

9 Fast Back to Back Enable (FBE) — RO. Hardwired to 0.

8

SERR# Enable (SERR_EN) — R/W.

0 = Enables SERR# generation.

1 = Disables SERR# generation.

7 Wait Cycle Control (WCC) — RO. Hardwired to 0.

6

Parity Error Response (PER) — R/W.

0 = Disable

1 = Sets Detected Parity Error bit (D31:F3:06, bit 15) when a parity error is detected.

5 VGA Palette Snoop (VPS) — RO. Hardwired to 0.

4 Postable Memory Write Enable (PMWE) — RO. Hardwired to 0.

3 Special Cycle Enable (SCE) — RO. Hardwired to 0.

2 Bus Master Enable (BME) — RO. Hardwired to 0.

1

Memory Space Enable (MSE) — R/W.

0 = Disables memory mapped config space.

1 = Enables memory mapped config space.

0

I/O Space Enable (IOSE) — R/W.

0 = Disable

1 = Enables access to the SMBus I/O space registers as defined by the Base Address

Register.

Loading...

Loading...