Datasheet 869

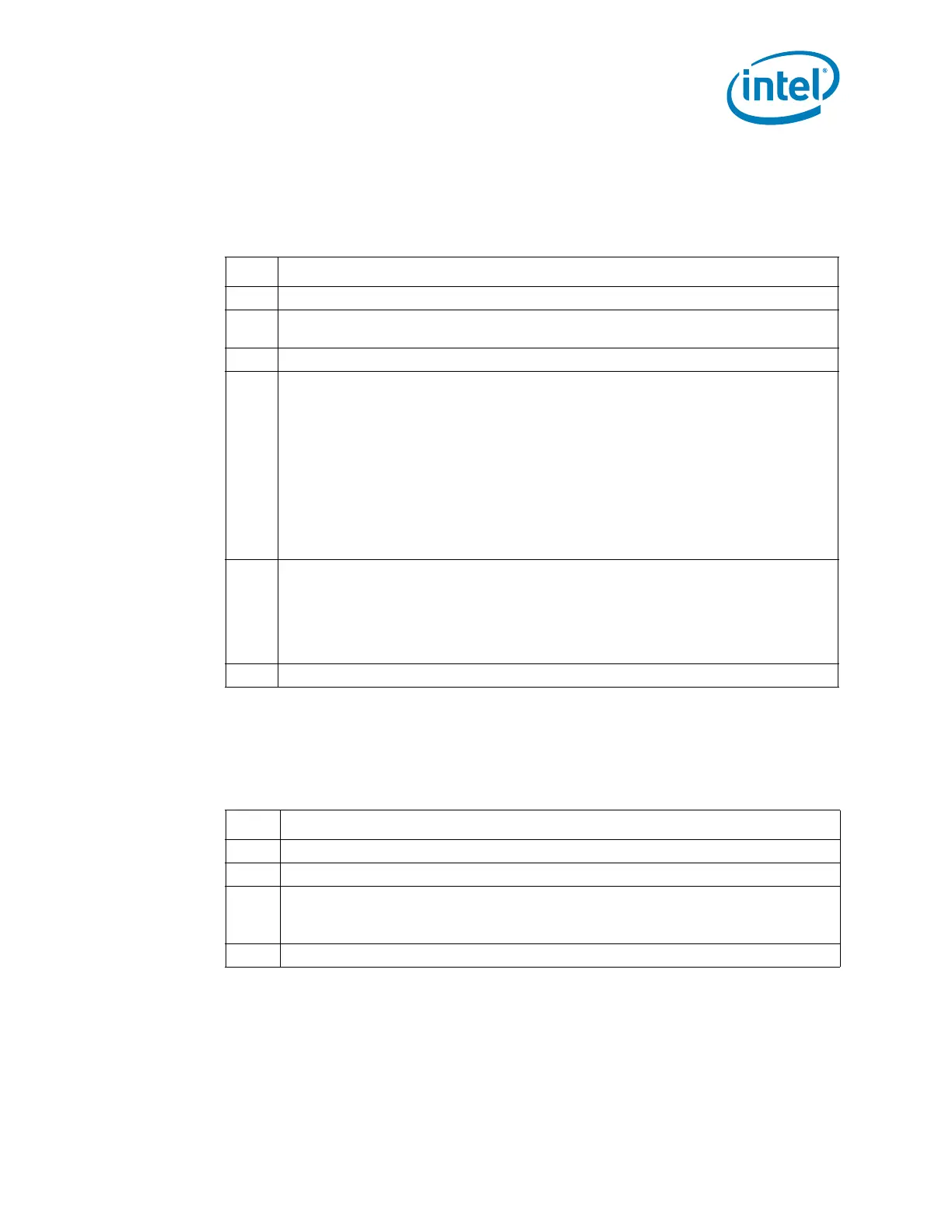

Intel® Management Engine Interface (MEI) Subsystem Registers (D22:F0)

23.1.3 PCICMD—PCI Command Register

(MEI—D22:F0)

Address Offset: 04h–05h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

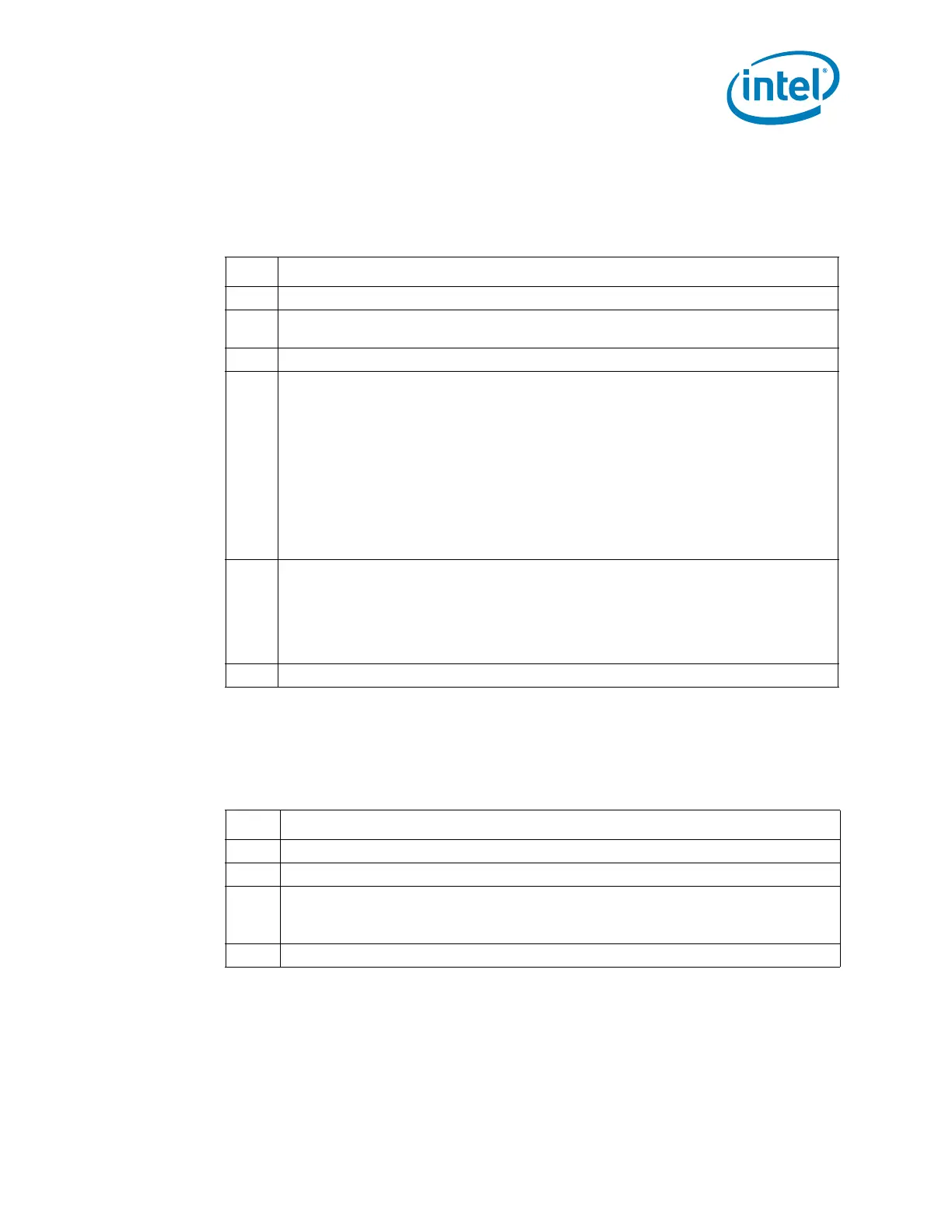

23.1.4 PCISTS—PCI Status Register

(MEI—D22:F0)

Address Offset: 06h–07h Attribute: RO

Default Value: 0010h Size: 16 bits

Bit Description

15:11 Reserved

10

Interrupt Disable (ID) — R/W. Disables this device from generating PCI line based

interrupts. This bit does not have any effect on MSI operation.

9:3 Reserved

2

Bus Master Enable (BME)— R/W.

Controls the Intel MEI host controller's ability to act as a system memory master for

data transfers. When this bit is cleared, Intel ME bus master activity stops and any

active DMA engines return to an idle condition. This bit is made visible to firmware

through the H_PCI_CSR register, and changes to this bit may be configured by the

H_PCI_CSR register to generate an ME MSI. When this bit is 0, Intel MEI is blocked

from generating MSI to the host processor.

NOTE: This bit does not block Intel MEI accesses to ME-UMA; that is, writes or reads to

the host and ME circular buffers through the read window and write window

registers still cause ME backbone transactions to ME-UMA.

1

Memory Space Enable (MSE) — R/W. Controls access to the Intel ME's memory

mapped register space.

0 = Disable. Memory cycles within the range specified by the memory base and limit

registers are master aborted.

1 = Enable. Allows memory cycles within the range specified by the memory base and

limit registers accepted.

0 Reserved

Bit Description

15:5 Reserved

4 Capabilities List (CL) — RO. Indicates the presence of a capabilities list, hardwired to 1.

3

Interrupt Status (IS)

— RO. Indicates the interrupt status of the device.

0 = Interrupt is deasserted.

1 = Interrupt is asserted.

2:0 Reserved

Loading...

Loading...