Datasheet 871

Intel® Management Engine Interface (MEI) Subsystem Registers (D22:F0)

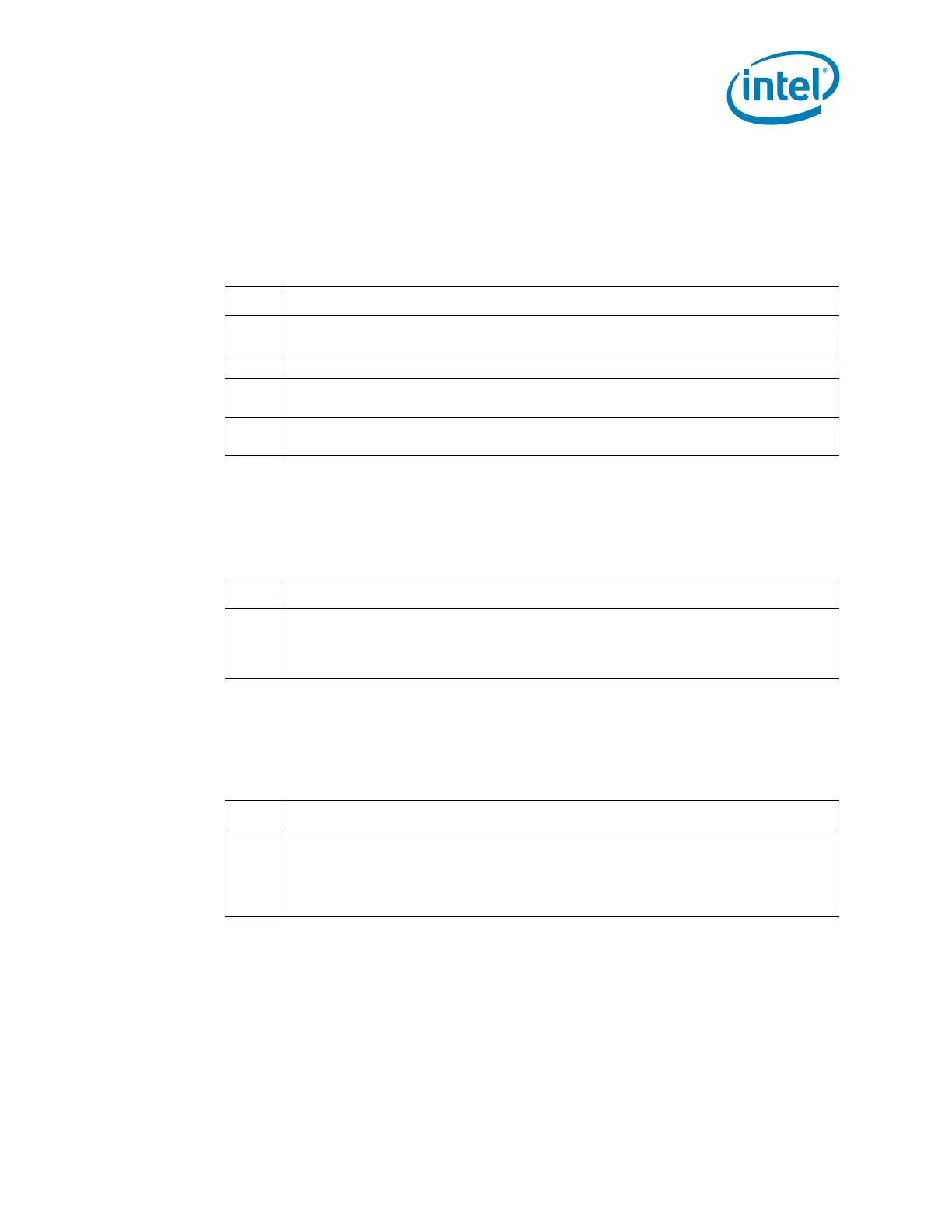

23.1.8 MEI0_MBAR—MEI0 MMIO Base Address Register

(MEI—D22:F0)

Address Offset: 10h–17h Attribute: R/W, RO

Default Value: 0000000000000004h Size: 64 bits

This register allocates space for the MEI0 memory mapped registers.

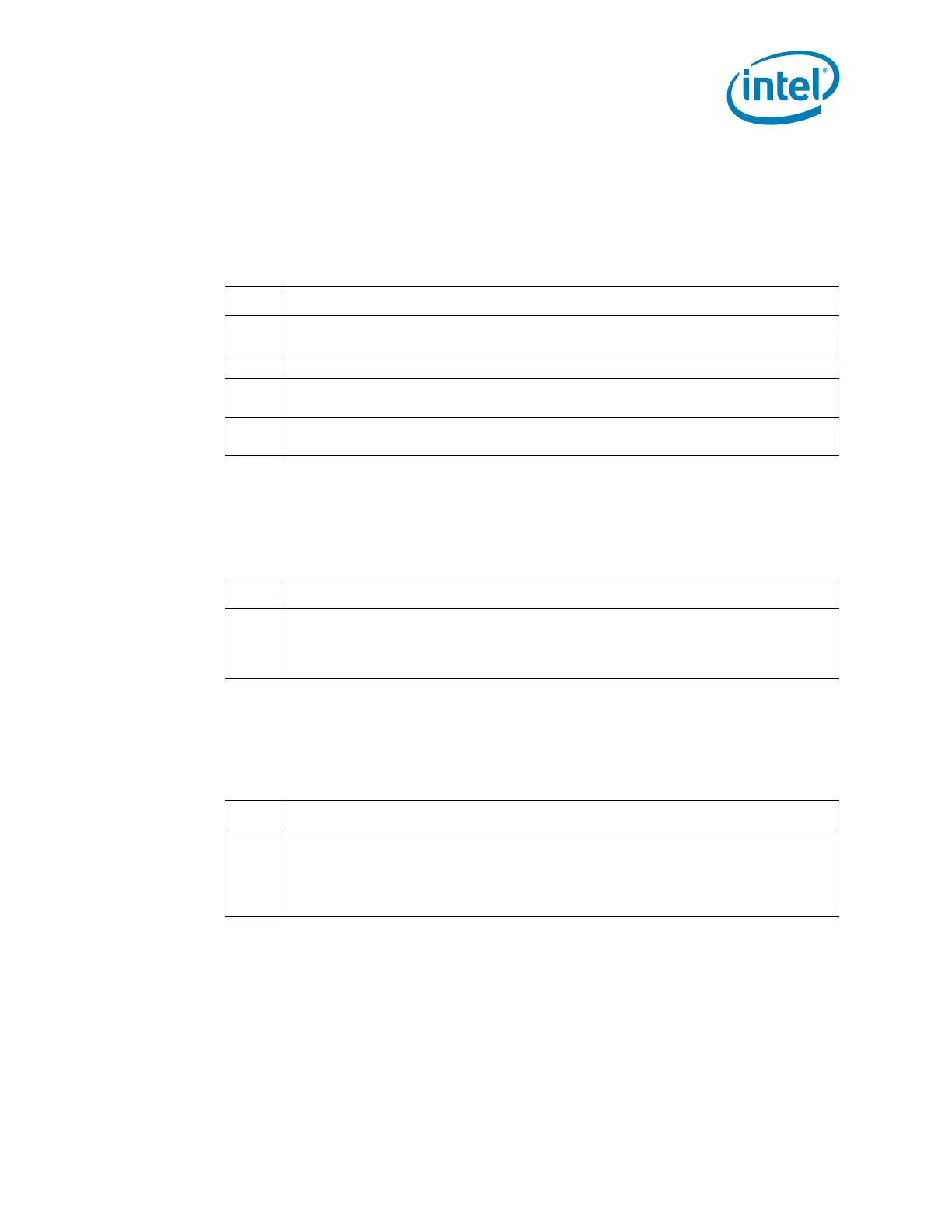

23.1.9 SVID—Subsystem Vendor ID Register

(MEI—D22:F0)

Address Offset: 2Ch–2Dh Attribute: R/WO

Default Value: 0000h Size: 16 bits

23.1.10 SID—Subsystem ID Register

(MEI—D22:F0)

Address Offset: 2Eh–2Fh Attribute: R/WO

Default Value: 0000h Size: 16 bits

Bit Description

63:4

Base Address (BA) — R/W. Software programs this field with the base address of

this region.

3 Prefetchable Memory (PM) — RO. Indicates that this range is not pre-fetchable.

2:1

Type (TP) — RO. Set to 10b to indicate that this range can be mapped anywhere in

64-bit address space.

0

Resource Type Indicator (RTE) — RO. Indicates a request for register memory

space.

Bit Description

15:0

Subsystem Vendor ID (SSVID) — R/WO. Indicates the sub-system vendor

identifier. This field should be programmed by BIOS during boot-up. Once written, this

register becomes Read Only. This field can only be cleared by PLTRST#.

NOTE: Register must be written as a Word write or as a DWord write with SID register.

Bit Description

15:0

Subsystem ID (SSID) — R/WO. Indicates the sub-system identifier. This field should

be programmed by BIOS during boot-up. Once written, this register becomes Read

Only. This field can only be cleared by PLTRST#.

NOTE: Register must be written as a Word write or as a DWord write with SVID

register.

Loading...

Loading...