5.151

Date Code 20171021 Instruction Manual SEL-421 Relay

Protection Functions

Circuit Breaker Failure Protection

Retrip Scheme Y2 Three Pole (Setting EBFL = Y2)

The logic shown in Figure 5.110 applies to three-pole breaker configurations.

Scheme Y2 is similar to Scheme 2, but the current check (50FA1) is now part of

the Retrip Time delay (RTPU1).

Retrip Scheme 2 Single Pole (Setting EBFL = 2)

Figure 5.111 illustrates the current-supervised single-pole retrip logic

(EBFL = 2). Timer RTPU1 (Breaker 1 Retrip Time Delay on Pickup Timer)

begins timing when initiation Relay Word bit BFIA1 asserts. Relay Word bit

RTA1 (Breaker 1 A-Phase Retrip) asserts immediately after timer RTPU1

expires. You can use just the RTA1 output for single-pole retrip without current

supervision. Relay Word bit RTSA1 (Breaker 1 Current Supervised A-Phase

Retrip) asserts if 50FA1 is picked up.

Figure 5.109 Scheme 2 Current-Supervised Three-Pole Retrip Logic

50FA1

50FB1

50FC1

BFIA1

RTS3P1

RT1

RT3P1

(Relay Word Bit)

BFIB1

BFIC1

RTSA1

RTSB1

RTSC1

Relay

Word

Bits

Relay

Word

Bit

SELOGIC

Settings

RT3PPU1

0

2 of 3

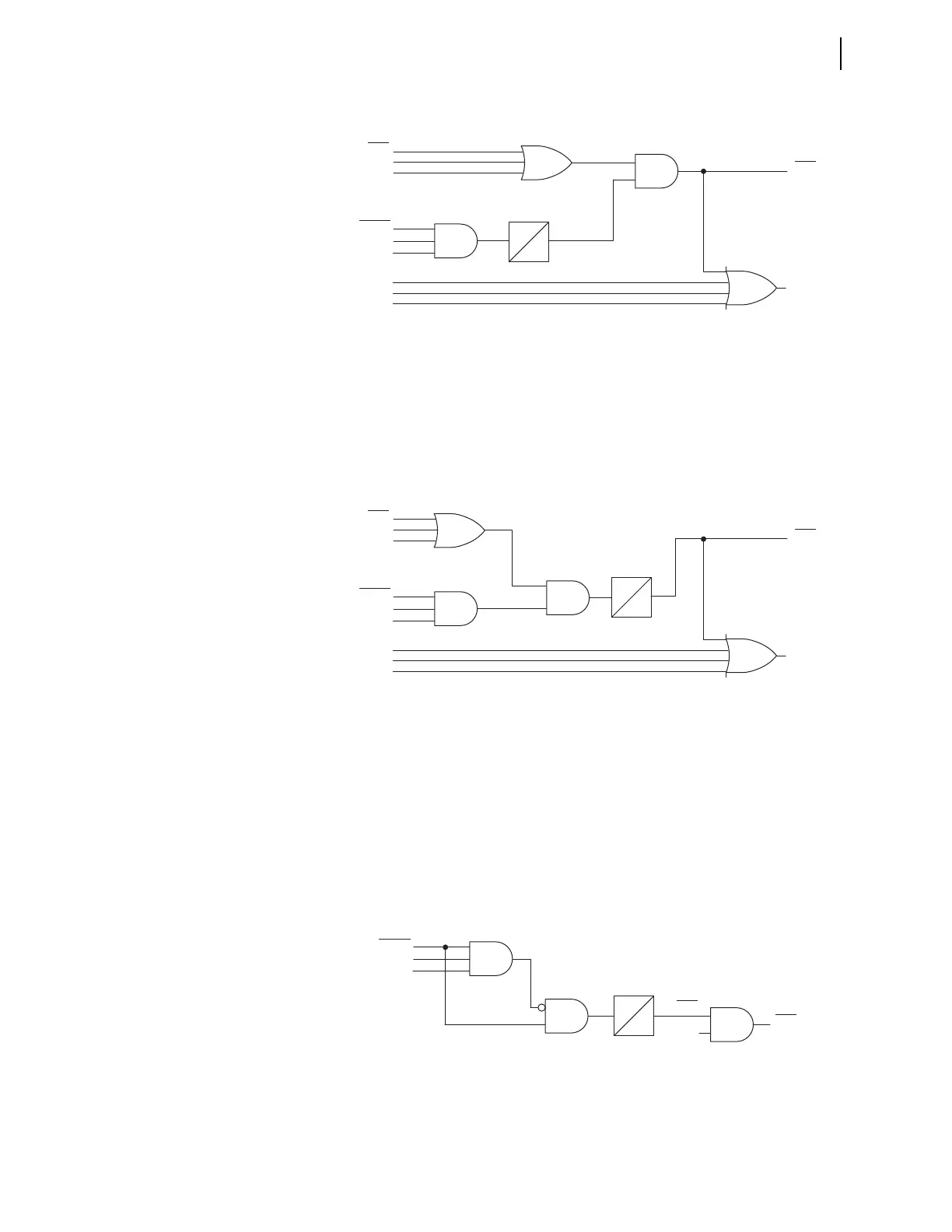

Figure 5.110 Scheme Y2 Current-Supervised Three-Pole Retrip Logic

50FA1

50FB1

50FC1

BFIA1

RTS3P1

RT1

BFIB1

BFIC1

RTSA1

RTSB1

RTSC1

Relay

Word

Bits

Relay

Word

Bit

SEL

OGIC

Settings

RT3PPU1

0

2 of 3

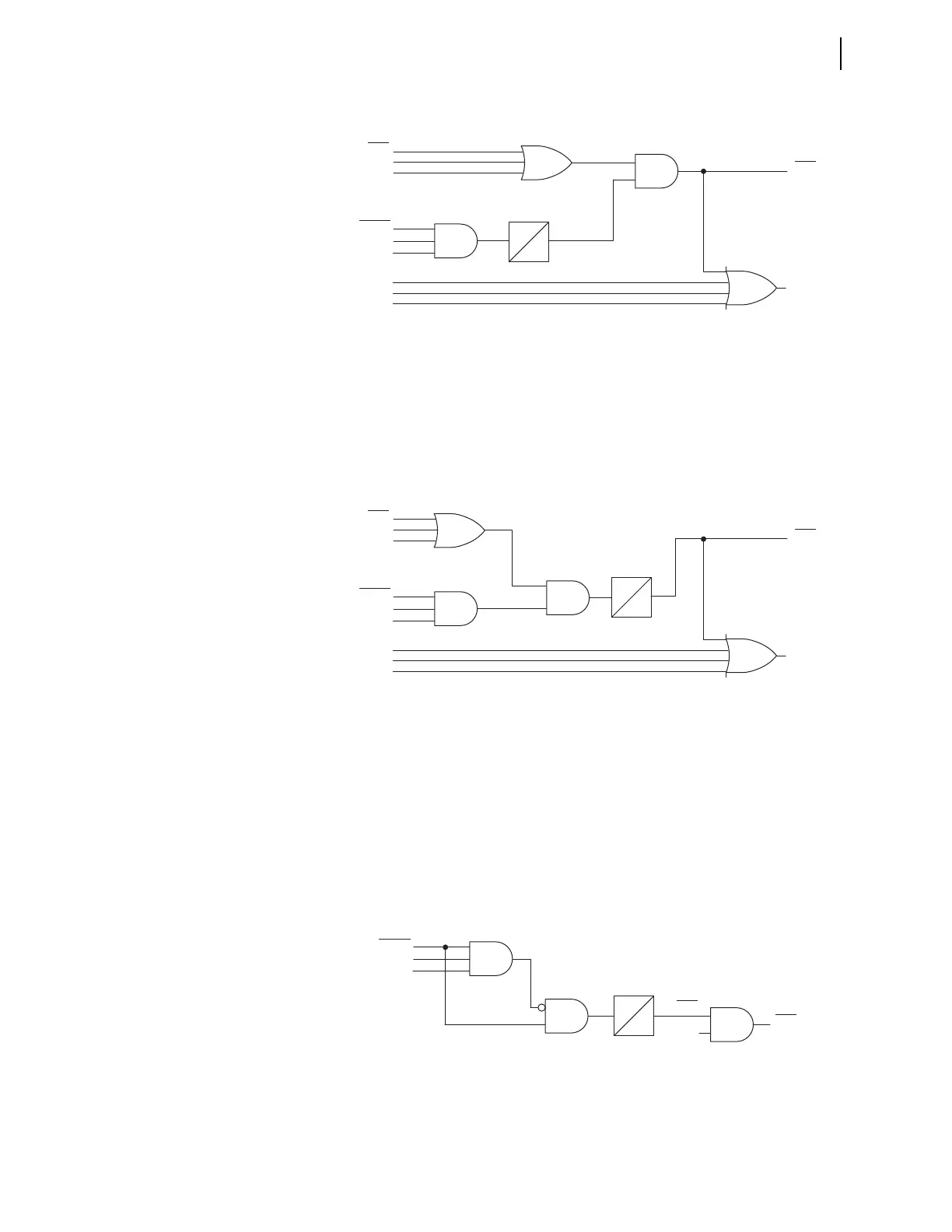

Figure 5.111 Scheme 2 Current-Supervised Single-Pole Retrip Logic

BFIA1

BFIB1

BFIC1

RTA1

50FA1

RTSA1

Relay

Word

Bit

Relay

Word

Bits

SELOGIC

Settings

RTPU1

0

2 of 3

Loading...

Loading...