11.65

Date Code 20171021 Instruction Manual SEL-421 Relay

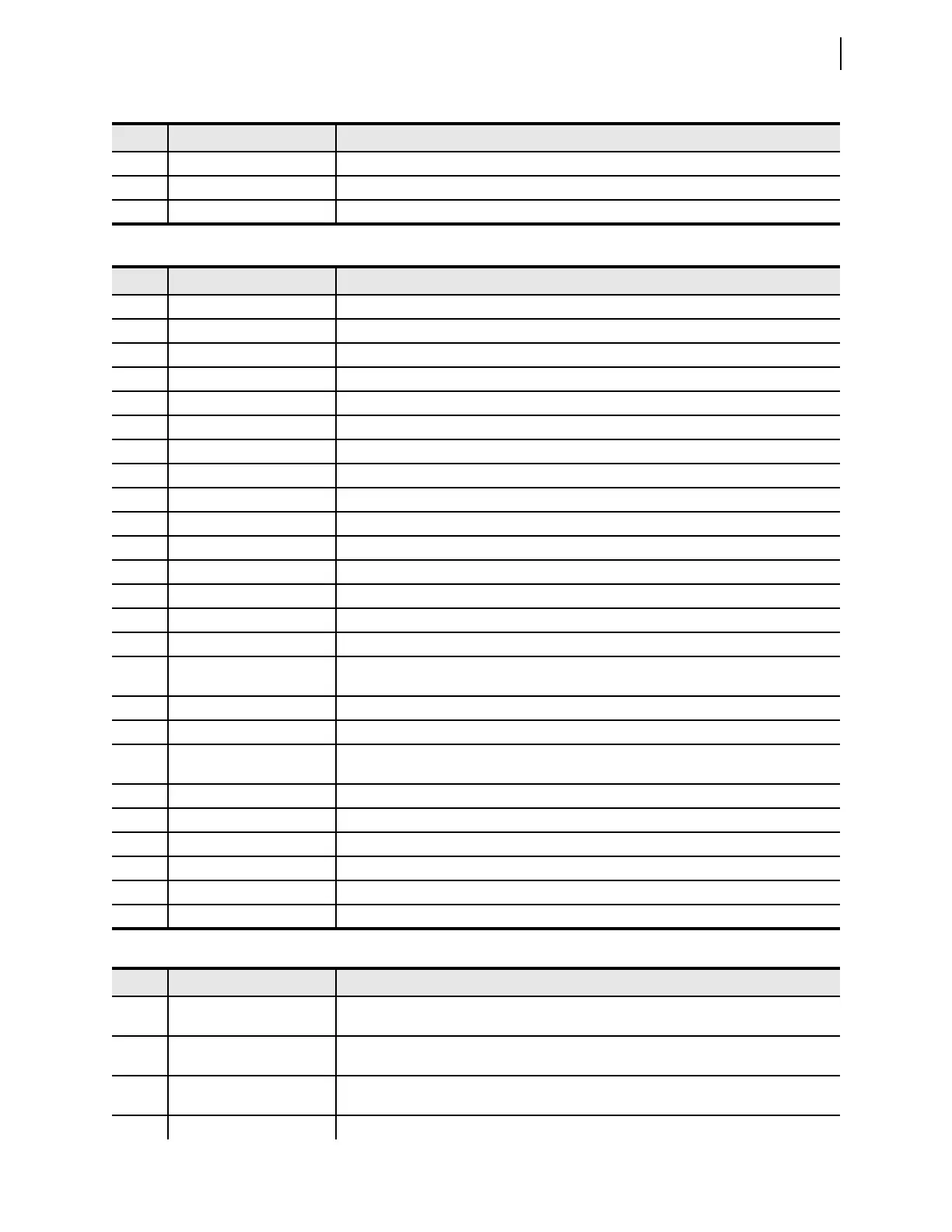

Relay Word Bits

Row Lists

291 RTCROKA Valid aligned RTC data available on Channel A

291 RTCENB Valid remote synchrophasors received on Channel B

291 RTCENA Valid remote synchrophasors received on Channel A

Table 11.57 Relay Word Bits: IRIG-B Control

Row Name Description

292 YEAR80 IRIG-B year information, binary-coded-decimal, add 80 if asserted

292 YEAR40 IRIG-B year information, binary-coded-decimal, add 40 if asserted

292 YEAR20 IRIG-B year information, binary-coded-decimal, add 20 if asserted

292 YEAR10 IRIG-B year information, binary-coded-decimal, add 10 if asserted

292 YEAR8 IRIG-B year information, binary-coded-decimal, add 8 if asserted

292 YEAR4 IRIG-B year information, binary-coded-decimal, add 4 if asserted

292 YEAR2 IRIG-B year information, binary-coded-decimal, add 2 if asserted

292 YEAR1 IRIG-B year information, binary-coded-decimal, add 1 if asserted

293 * Reserved

293 * Reserved

293 TUTCH IRIG-B Offset half-hour from UTC time, binary, add 0.5 if asserted

293 TUTC8 IRIG-B Offset hours from UTC time, binary, add 8 if asserted

293 TUTC4 IRIG-B Offset hours from UTC time, binary, add 4 if asserted

293 TUTC2 IRIG-B Offset hours from UTC time, binary, add 2 if asserted

293 TUTC1 IRIG-B Offset hours from UTC time, binary, add 1 if asserted

293 TUTCS IRIG-B Offset hours sign from UTC time, subtract the UTC offset if TUTCS is asserted, add

otherwise

294 DST Daylight saving time

294 DSTP IRIG-B Daylight saving time pending

294 LPSEC Direction of the upcoming leap second. During the time that LPSECP is asserted, if LPSEC is

asserted, the upcoming leap second is deleted; otherwise, the leap second is added.

294 LPSECP Leap second pending

294 TQUAL8 Time quality, binary, add 8 when asserted

294 TQUAL4 Time quality, binary, add 4 when asserted

294 TQUAL2 Time quality, binary, add 2 when asserted

294 TQUAL1 Time quality, binary, add 1 when asserted

295 * Reserved

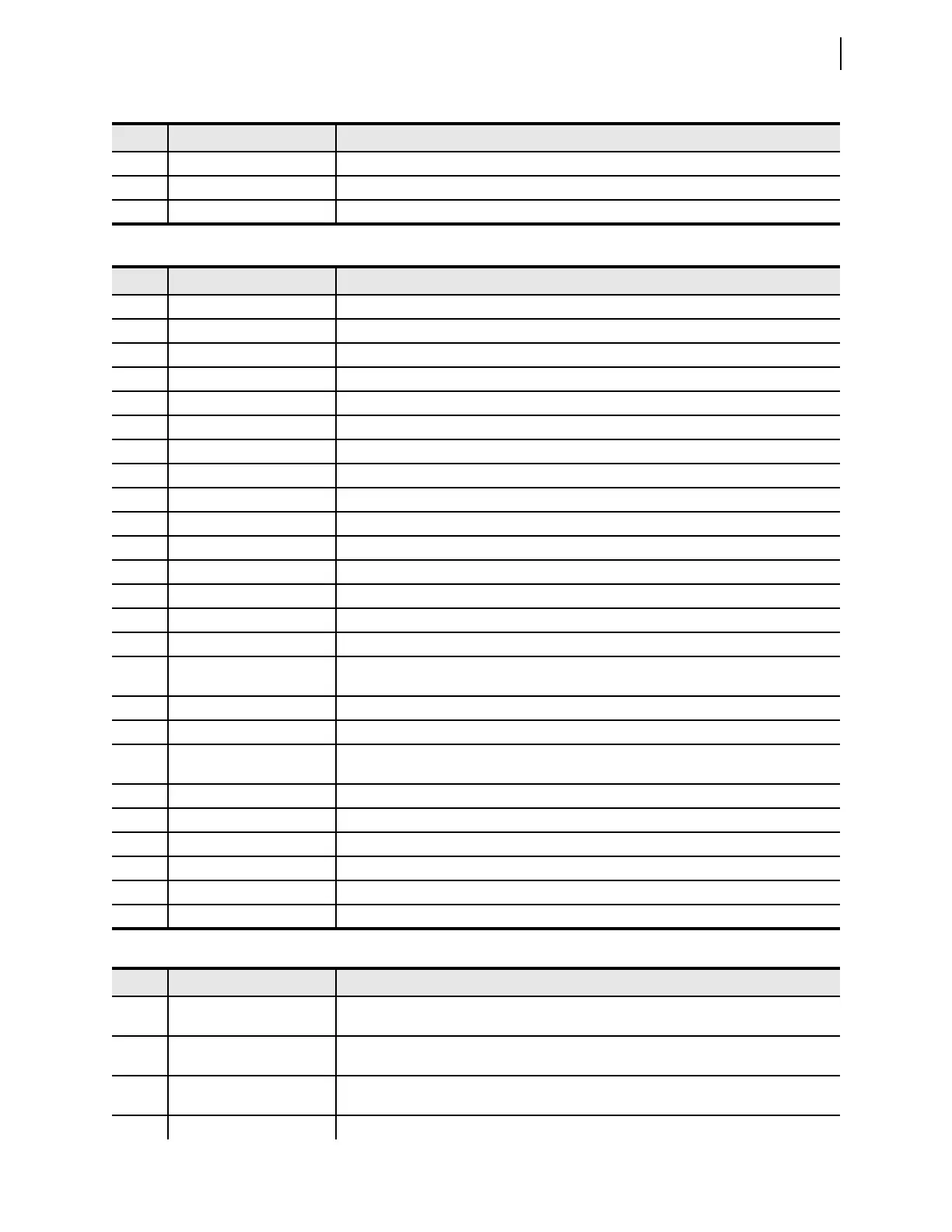

Table 11.58 Relay Word Bit: Time-Error Calculation (Sheet 1 of 2)

Row Name Description

296 LOADTE Load TECORR factor (SELOGIC Equation). When a rising-edge is detected, the accumulated

time-error value TE is loaded with the TECORR factor (preload value).

296 STALLTE Stall time-error calculation (SEL

OGIC Equation). When asserted, the time-error calculation is

stalled, or frozen.

296 PLDTE Asserts for approximately 1.5 cycles when the TEC command is used to load a new time-

error correction factor (preload value) into the TECORR analog quantity.

296 * Reserved

Table 11.56 Relay Word Bits: Synchrophasor SEL

OGIC Equations/RTC Synchrophasors Status Bits (Sheet 2 of 2)

Row Name Description

Loading...

Loading...