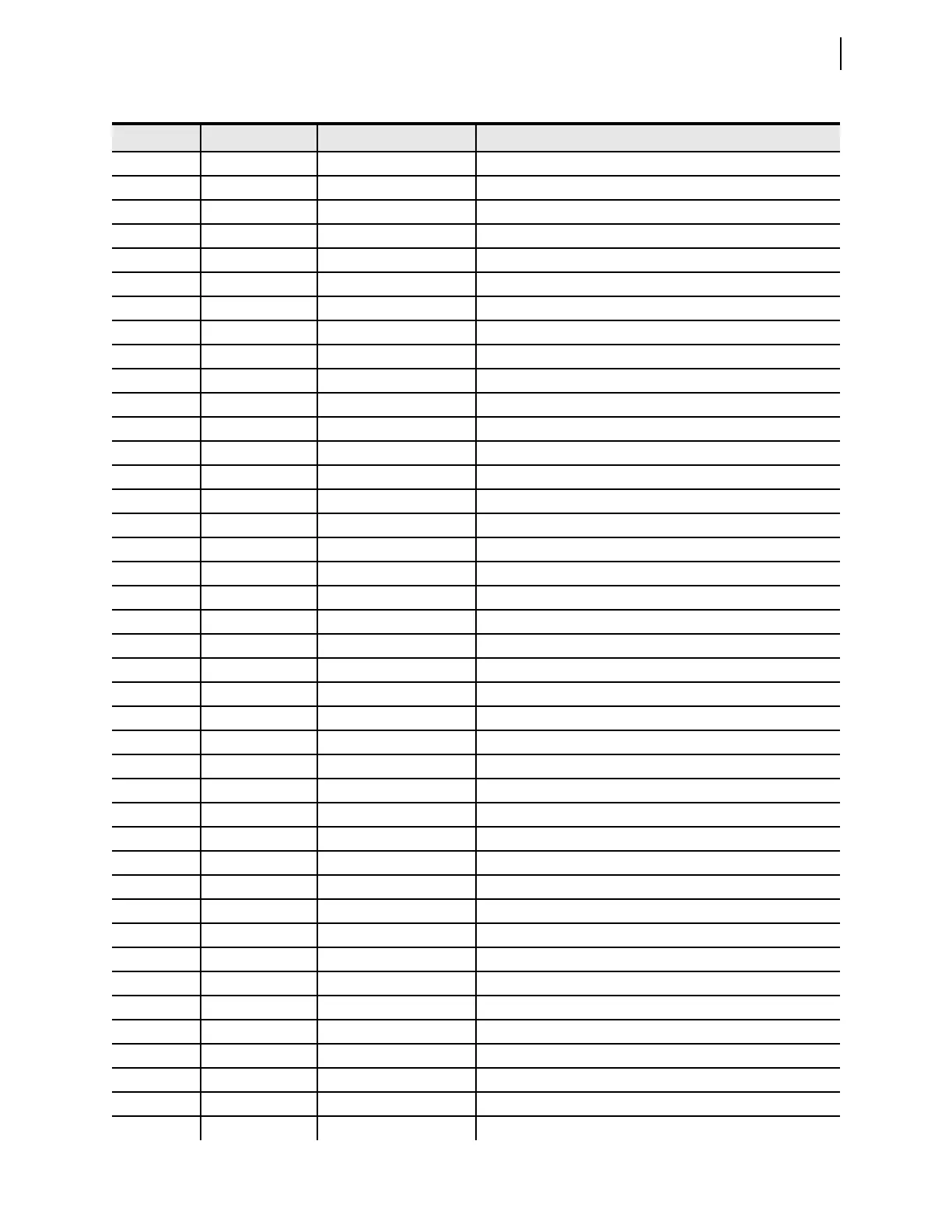

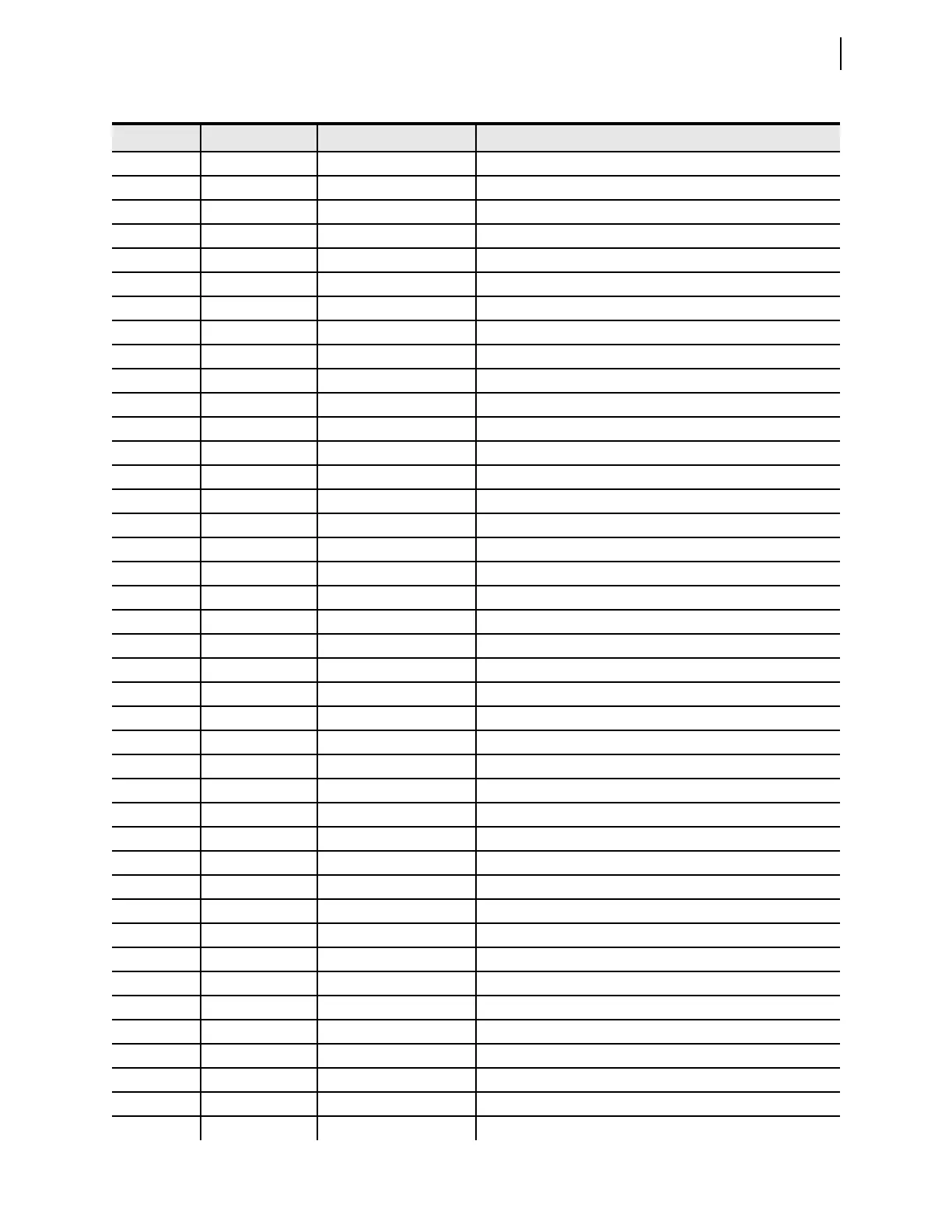

10.25

Date Code 20171021 Instruction Manual SEL-421 Relay

Communications Interfaces

IEC 61850 Communication

G1PTOC2 Str.general 67G1

a

Level 1 residual directional overcurrent element

G2PIOC5 Op.general 50G2

a

Level 2 residual overcurrent element

G2PTOC5 Op.general 67G2T

a

Level 2 residual delayed directional overcurrent element

G2PTOC5 Str.general 67G2

a

Level 2 residual directional overcurrent element

G3PIOC8 Op.general 50G3

a

Level 3 residual overcurrent element

G3PTOC8 Op.general 67G3T

a

Level 3 residual delayed directional overcurrent element

G3PTOC8 Str.general 67G3

a

Level 3 residual directional overcurrent element

G4PIOC11 Op.general 50G4

a

Level 4 residual overcurrent element

G4PTOC11 Op.general 67G4T

a

Level 4 residual delayed directional overcurrent element

G4PTOC11 Str.general 67G4

a

Level 4 residual directional overcurrent element

OSB1RPSB2 BlkZn.stVal OSB1

a

Block Zone 1 during an out-of-step condition

OSB1RPSB2 Str.general OSB

a

Out-of-step block

OSB2RPSB3 BlkZn.stVal OSB2

a

Block Zone 2 during an out-of-step condition

OSB2RPSB3 Str.general OSB

a

Out-of-step block

OSB3RPSB4 BlkZn.stVal OSB3

a

Block Zone 3 during an out-of-step condition

OSB3RPSB4 Str.general OSB

a

Out-of-step block

OSB4RPSB5 BlkZn.stVal OSB4

a

Block Zone 4 during an out-of-step condition

OSB4RPSB5 Str.general OSB

a

Out-of-step block

OSB5RPSB6 BlkZn.stVal OSB5

a

Block Zone 5 during an out-of-step condition

OSB5RPSB6 Str.general OSB

a

Out-of-step block

OSTRPSB1 Op.general OST

a

Out-of-step tripping

P1PIOC1 Op.general 50P1

a

Level 1 phase overcurrent element

P1PTOC1 Op.general 67P1T

a

Level 1 phase-delayed directional overcurrent element

P1PTOC1 Str.general 67P1

a

Level 1 phase directional overcurrent element

P2PIOC4 Op.general 50P2

a

Level 2 phase overcurrent element

P2PTOC4 Op.general 67P2T

a

Level 2 phase-delayed directional overcurrent element

P2PTOC4 Str.general 67P2

a

Level 2 phase directional overcurrent element

P3PIOC7 Op.general 50P3

a

Level 3 phase overcurrent element

P3PTOC7 Op.general 67P3T

a

Level 3 phase-delayed directional overcurrent element

P3PTOC7 Str.general 67P3

a

Level 3 phase directional overcurrent element

P4PIOC10 Op.general 50P4

a

Level 4 phase overcurrent element

P4PTOC10 Op.general 67P4T

a

Level 4 phase-delayed directional overcurrent element

P4PTOC10 Str.general 67P4

a

Level 4 phase directional overcurrent element

POTTPSCH1 EchoWei.stVal EKEY

a

Echo received permissive trip signal

POTTPSCH1 EchoWeiOp.stVal ECTT

a

Echo conversion to trip signal

POTTPSCH1 Op.general RXPRM

a

Receiver trip permission

POTTPSCH1 RxPrm1.general PTRX

a

Permissive trip received Channel 1 and Channel 2

POTTPSCH1 TxBlk.general Z3RB

a

Current reversal guard asserted

POTTPSCH1 TxPrm.general KEY

a

Transmit permissive trip signal

Q1PIOC3 Op.general 50Q1

a

Level 1 negative-sequence overcurrent element

Q1PTOC3 Op.general 67Q1T

a

Level 1 negative sequence delayed directional overcurrent element

Table 10.15 Logical Device: PRO (Protection) (Sheet 4 of 6)

Logical Node Attribute Data Source Comment

Loading...

Loading...