PCH Pin States

106 Datasheet

NOTES:

1. The states of Core and processor signals are evaluated at the times During PLTRST# and

Immediately after PLTRST#. The states of the Controller Link signals are taken at the

times During CL_RST1# and Immediately after CL_RST1#. The states of the Suspend

signals are evaluated at the times During RSMRST# and Immediately after RSMRST#, with

an exception to GPIO signals; refer to Section 2.24 for more details on GPIO state after

reset. The states of the HDA signals are evaluated at the times During HDA_RST# and

Immediately after HDA_RST#.

2. SLP_S5# signal will be high in the S4 state and low in the S5 state.

3. Low until Intel

®

High Definition Audio Controller Reset bit set (D27:F0:Offset

HDBAR+08h:bit 0), at which time HDA_RST# will be High and HDA_BIT_CLK will be

Running.

4. PETp/n[8:1] low until port is enabled by software.

5. The SLP_A# state will be determined by Intel ME Policies.

6. The state of signals in S3-5 will be defined by Intel ME Policies.

7. This signal is sampled as a functional strap During Reset. Refer to Functional straps

definition table for usage.

8. Native functionality multiplexed with these GPIOs is not utilized in Mobile Configurations.

9. Native/GPIO functionality controlled using soft straps. Default to Native functionality until

soft straps are loaded.

10. This pin will be driven to a High when Dock Attach bit is set (Docking Control Register

D27:F0 Offset 4Ch)

11. This pin will be driven to a Low when Dock Attach bit is set (Docking Control Register

D27:F0 Offset 4Ch)

12. PCH tri-states these signals when LVDS port is disabled.

13. Controller Link Clock and Data buffers use internal pull-up and pull-down resistors to drive

a logical 1 or a 0.

14. SLP_LAN# behavior after reset is dependent on value of SLP_LAN# default value bit. A

soft-strap is used to select between SLP_LAN# and GPIO usage. When strap is set to 0

(default), pin is used as SLP_LAN#, when soft-strap is set to 1, pin is used as GPIO29.

15. State of the pins depend on the source of VccASW power.

16. Pin state reflected when SPI2 enable RTC power backed soft strap is enabled, for Mobile

configurations using a Finger-Print Sensor device. When soft strap is not enabled, signal

defaults to GP Input.

17. Based on Intel ME wake events and Intel ME state. SUSPWRDNACK is the default mode of

operation. If system supports Deep S4/S5, subsequent boots will default to SUSWARN#

18. Pins are tri-stated prior to APWROK assertion During Reset.

19. CLKRUN# is driven to a logic 1 During Reset for Mobile configurations (default is native

function) to ensure that PCI clocks can toggle before devices come out of Reset.

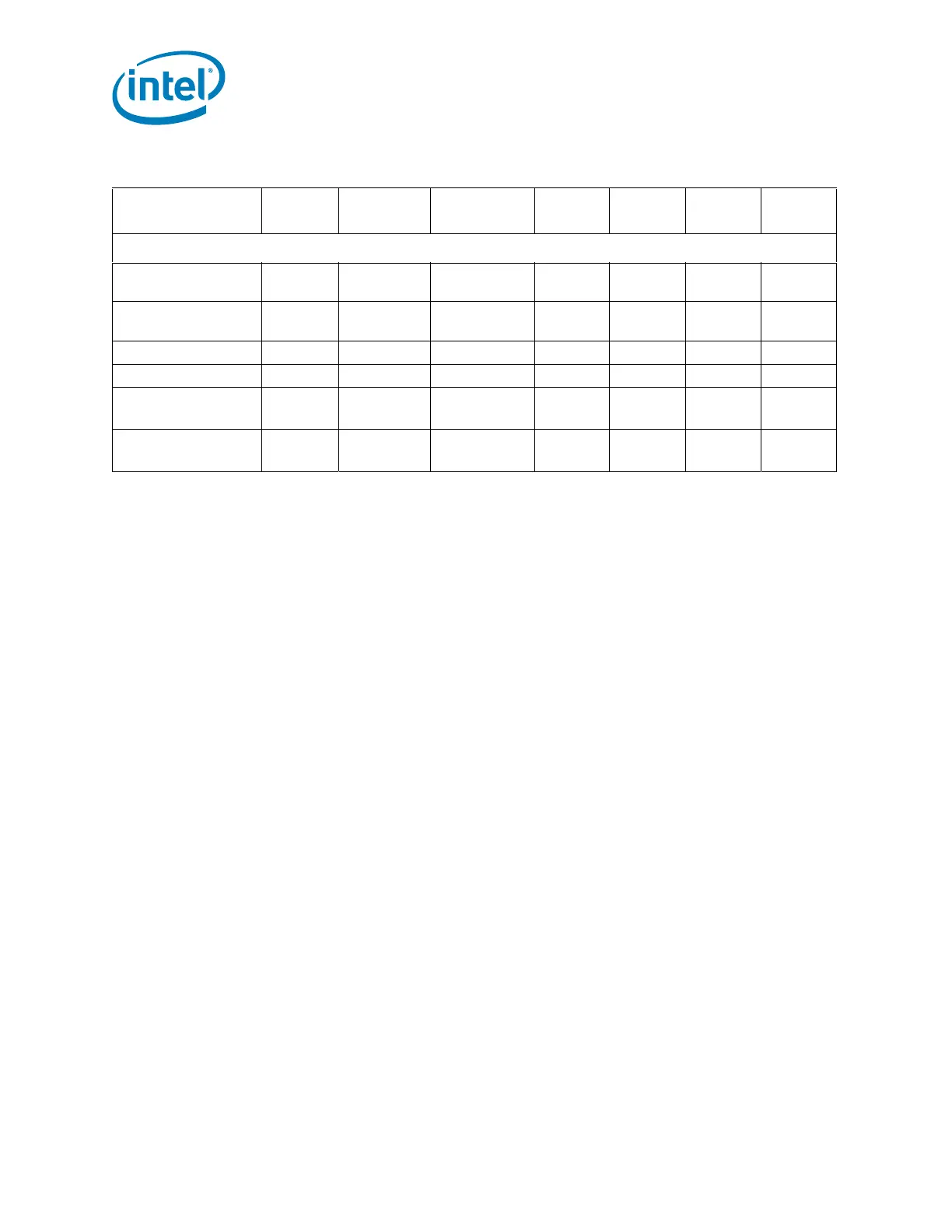

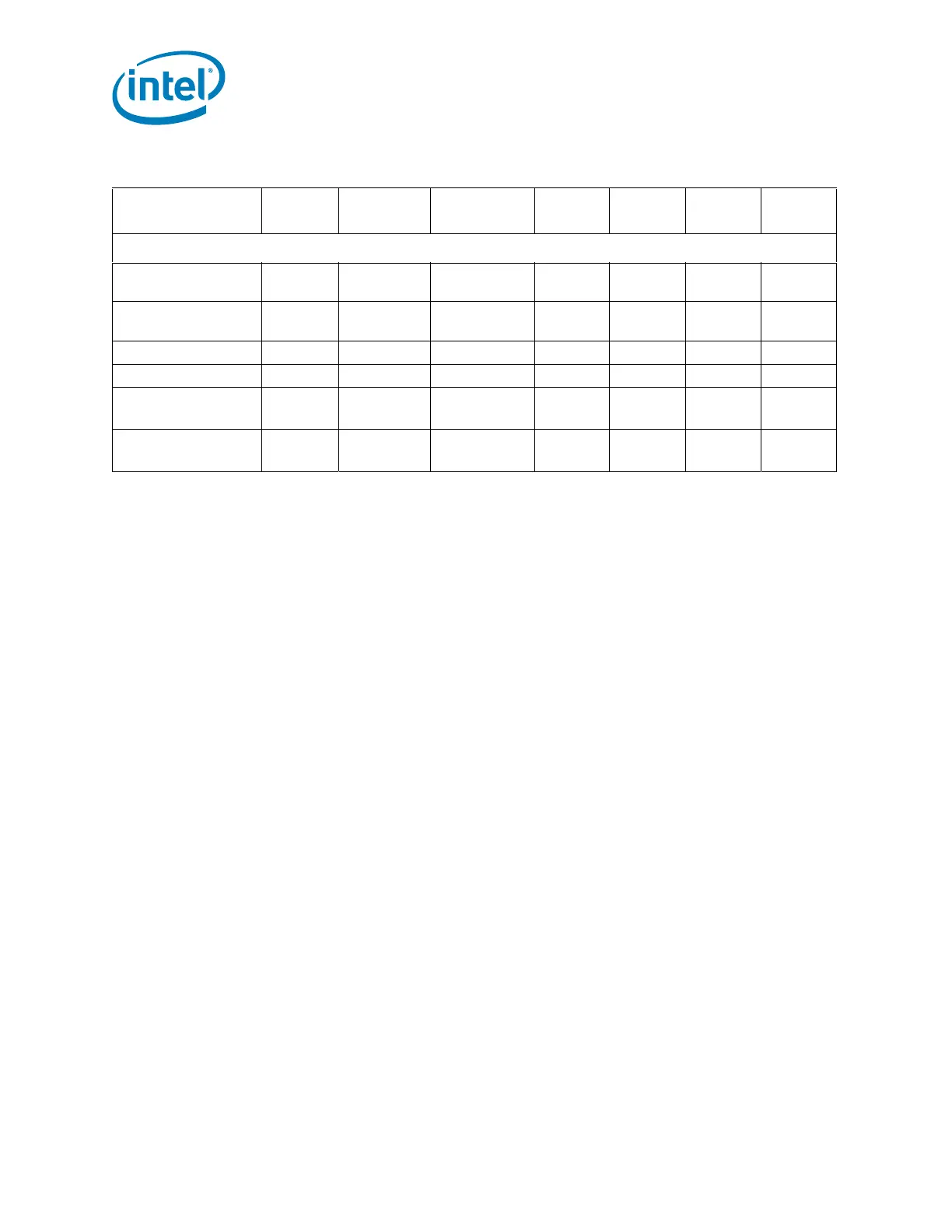

Digital Display Interface

DDP[D:B]_[3:0]P,

DDP[D:B]_[3:0]N,

Core Low Low Defined Defined Off Off

DDP[D:B]_AUXP,

DDP[D:B]_AUXN

Core Low Low Defined Defined Off Off

SDVO_CTRLCLK Core High-Z High-Z Defined Defined Off Off

SDVO_CTRLDATA Core Low High-Z Defined Defined Off Off

DDPC_CTRLCLK,

DDPD_CTRLCLK

Core High-Z High-Z Defined Defined Off Off

DDPC_CTRLDATA,

DDPD_CTRLDATA

Core Low High-Z Defined Defined Off Off

Table 3-3. Power Plane and States for Output and I/O Signals for Mobile Configurations

(Sheet 6 of 6)

Signal Name

Power

Plane

During

Reset

1

Immediately

after Reset

1

C-x

states

S0/S1 S3 S4/S5

Loading...

Loading...